新聞動態

SiLabs的目標是具有低抖動時鐘芯片的56Gbit / s通信

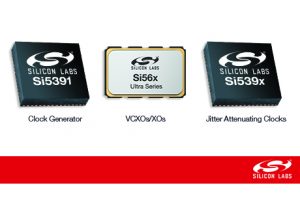

Si5391是一款“任意頻率”時鐘發生器,具有多達12個輸出和低於100fs的RMS相位抖動。

精密校準版(“P級”)通常可實現69fs RMS相位抖動,並可創建56Gbit / s serdes設計所需的主要頻率。該公司將其描述為“真正的低於100 fs時鍾樹的芯片”,滿足56G PAM-4參考時鐘抖動要求和裕量。

Si5395 / 4/2是用於互聯網基礎設施的抖動衰減器,可以從任何輸入頻率產生任何輸出頻率組合,同時提供90fs RMS相位抖動。 P級器件再次提供69fs RMS典型相位抖動。

Si56x的“Ultra系列”VCXO和XO系列可定制至高達3GHz的任何頻率,支持兩倍於之前Silicon Labs VCXO產品的工作頻率範圍,具有一半的抖動。

它們採用5 x 7mm和3.2 x 5mm版本的單,雙,四和I2C可編程選項。使用標準封裝意味著它們將丟棄早期XO,VCXO和VCSO佔用的一些插槽。典型的相位抖動低至90fs。

Si54x Ultra系列XO系列適用於要求更高穩定性和長期可靠性保證的應用,如光傳輸網絡(OTN),寬帶設備,數據中心和工業系統。

它們專為56Gbit / s PAM-4(四電平脈衝幅度調製)而設計,可在保持帶寬恆定的同時提高每個通道的比特率。典型的相位抖動低至80 fs。