新聞動態

DAC探討了AI和ML在市場中的作用

舊金山Moscone中心將於6月25日至28日舉辦DAC

OneSpin解決方案 和 Austemper設計系統 將突出強調功能安全驗證的工具。 Austemper將專注於關鍵任務系統開發,KaleidoScope工具套件支持並發混合信號故障傳播的模擬設計。自動化工具套件具有面向認證的應用程序的安全分析,綜合和驗證功能。它用於ADAS和自動駕駛中的大規模汽車設計。並發故障模擬包括ISO 26262推薦的符合ASIL要求的模擬。

該公司最近與OneSpin Solutions合作,採用工具支持的功能安全應用方法,結合設計和驗證流程,將在OneSpin展台展示。芯片設計中插入了硬件安全機制,OneSpin Solutions的工具正式驗證了硬件安全邏輯。等效性檢查可確保插入的安全邏輯不會影響常規功能,故障檢測分析可驗證安全機制在發生隨機錯誤時是否正常運行。

在TÜV南德意志集團對其工具開發流程進行驗證後,OneSpin還在推廣其工具認證套件。最初的套件可用於該公司的360 EC-FPGA EDA工具,這是一種自動順序等效性檢查,可防止FPGA設計流程引入實現錯誤。該套件已通過ISO 26262,IEC 61508和EN 50128認證。

FPGA見解

仍採用FPGA設計, Plunify 與Xilinx合作,通過Plunify雲平台在雲中提供Vivado設計套件。設計人員只需50c即可在Amazon Web Services(AWS)雲上編譯Vivado項目,包括許可證。

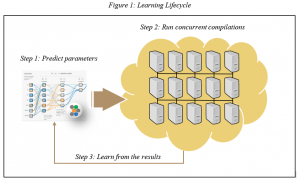

該公司還將展示其InTime時序收斂軟件的增強功能,以優化雲中的FPGA時序(圖1)。 InTime優化方法可以將時鐘頻率提高20%到80%,並通過機器學習在幾天內滿足時序要求,而不是幾週。該軟件還可加速時序收斂和優化,並可通過雲訪問。

該公司還將展示其InTime時序收斂軟件的增強功能,以優化雲中的FPGA時序(圖1)。 InTime優化方法可以將時鐘頻率提高20%到80%,並通過機器學習在幾天內滿足時序要求,而不是幾週。該軟件還可加速時序收斂和優化,並可通過雲訪問。

推廣eFPGA技術, Achronix Semiconductor 正在與知識產權專家合作 投 增加吞吐量並節省內存存儲空間。

兩家參展商將解釋CAST的無損壓縮IP如何移植到Achronix FPGA產品組合,用於數據中心和移動邊緣數據傳輸應用。 Deflate,GZIP和ZLIB的無損壓縮標準的硬件實現與用於壓縮或解壓縮的軟件實現兼容,提供高達100Gbit / s的吞吐量,低壓縮和低延遲,再加上Speedcore eFPGA技術,可以移動和存儲大量低功耗的數據。

CAST已將其IP移植到Achronix的FPGA

能源效率

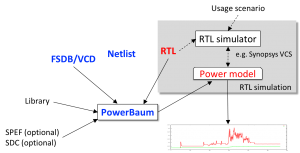

說到電源管理,另一個參展商, 鮑姆,將能效確定為芯片設計中最不發達的領域。其自動功率分析和建模工具專為汽車,物聯網,移動,網絡和服務器項目而設計。 PowerBaum 2.0(圖3)支持動態和靜態功耗,包括RTL和網表描述,並通過硬件仿真添加對功耗分析的支持。該公司稱,這使得工程師可以在現實的軟件場景中修復電源錯誤。該工具還支持設計人員指定的任意溫度分析,以評估溫度對設計功耗的影響。

在DAC,該公司還將推出PowerWurzel,一種與PowerBaum集成的門級功率分析引擎,用於功率建模。

圖3 Baum的工具分析能源效率

基於雲的SoC設計和驗證工具,用於IC設計 度量 包括Cloud Simulator和Verification Manager,旨在管理模擬要求和資源,每分鐘調高或調低一次。該公司聲稱,Google Cloud可以實現無限制的UVM兼容SystemVerilog仿真能力和基於Web的本地驗證管理,以實現更快的回歸時間,減少中繼代碼錯誤和可預測的代碼覆蓋率。

除了參展商外,該活動還舉辦技術會議和主題演講計劃。例如,今年,Cadence將主持一個關於“汽車應用的功能安全性和可靠性”的教程,以及一個關於機器學習的教程(“機器學習將語音識別性能提升到新的水平”)。 Instmental的Anna-Katrina Shedletsky將於6月25日週一發表主題演講,重點關注“智能自動化:機器學習和製造業的未來”。南加州大學的MajaMatarić將在周四的主題演講中探討使用ML和AI進行社會輔助機器人(SAR)的演講,他將介紹“自動化與增強:社會輔助Robotocs和工作的未來”。

另一個主題演講主張RISC-V作為從專有指令集架構(ISA)中釋放架構師的手段。谷歌和加州大學的David A Patterson將展示“計算機架構的新黃金時代:領域特定加速器和開放式RISC-V”。

今年DAC的一個新領域是設計基礎設施巷。該倡議由 ESD聯盟 和協會 適用於高性能計算專業人士 是一個致力於IT基礎設施的領域,用於設計電子系統和組件。除了設計和管理雲使用的計算和存儲要求外,還有一個專門的雲端設計展館,討論許可管理,網格計算和數據安全。