# LB11967V

## Monolithic Digital IC For Variable Speed Fan Motor Single-Phase Full-Wave Pre-Driver

http://onsemi.com

#### Overview

The LB11967V is a single-phase bipolar variable speed fan motor pre-driver that works with an external PWM signal. A highly efficient, quiet and low power consumption motor driver circuit, with a large variable speed, can be implemented by adding a small number of external components.

This device is optimal for driving large scale fan motors (with large air volume and large current) such as those used in servers and consumer products.

#### **Functions**

- Pre-driver for single-phase full-wave drive

- ⇒ PNP-EMOS is used as an external power Transistor, enabling high-efficiency low-consumption drive by means of the low-saturation output and single-phase full-wave drive. (PMOS-NMOS also applicable)

- External PWM input enabling variable speed control

- ⇒ Separately-excited upper direct PWM (f = 25kHz) control method, enabling highly silent speed control

- Compatible with 12V, 24V, and 48V power supplies

- Current limiter circuit incorporated

- ⇒ Chopper type current limit at start

- Reactive current cut circuit incorporated

- ⇒ Reactive current before phase change is cut to enable silent and low-consumption drive.

- Minimum speed setting pin

- ⇒ Minimum speed can be set with external resistor. The start assistance circuit enables start at extremely low speed.

- Constant-voltage output pin for Hall bias

- Lock protection and automatic reset functions incorporated

- (Rotation speed detection), RD (Lock detection) output

## **Specifications**

## **Maximum Ratings** at $Ta = 25^{\circ}C$

| Parameter                                 | Symbol                               | Conditions                    | Ratings     | Unit |

|-------------------------------------------|--------------------------------------|-------------------------------|-------------|------|

| V <sub>CC</sub> maximum supply voltage    | V <sub>CC</sub> max                  |                               | 18          | V    |

| OUT pin maximum output current            | I <sub>OUT</sub> max                 |                               | 50          | mA   |

| OUT pin output withstand voltage          | V <sub>OUT</sub> max                 |                               | 18          | V    |

| HB maximum output current                 | I <sub>HB</sub> max                  |                               | 10          | mA   |

| VTH input pin withstand voltage           | V <sub>VTH</sub> max                 |                               | 8           | V    |

| RD/FG output pin output withstand voltage | V <sub>RD</sub> /V <sub>FG</sub> max |                               | 18          | V    |

| RD/FG output current                      | I <sub>RD</sub> /I <sub>FG</sub> max |                               | 10          | mA   |

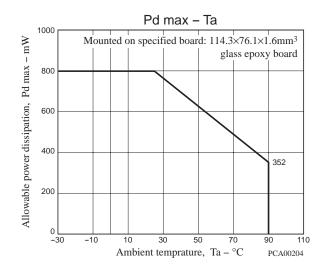

| Allowable power dissipation               | Pd max                               | Mounted on a specified board* | 800         | mW   |

| Operating temperature range               | Topr                                 |                               | -30 to +95  | °C   |

| Storage temperature range                 | Tstg                                 |                               | -55 to +150 | °C   |

<sup>\*</sup>Specified board: 114.3mm × 76.1mm × 1.6mm, glass epoxy board.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

### **Recommended Operating Conditions** at Ta = 25°C

| Parameter                      | Symbol | Conditions      | Ratings  | Unit |

|--------------------------------|--------|-----------------|----------|------|

| V <sub>CC</sub> supply voltage | VCC    |                 | 6 to 16  | V    |

| VTH input level voltage range  | VTH    | Full speed mode | 0 to 7   | V    |

| Hall input common phase input  | VICM   |                 | 0.2 to 3 | V    |

| voltage range                  |        |                 |          |      |

### **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 12V$ , unless otherwise specified.

| Parameter                          | Cumb al                            | Conditions                                        |      | Ratings     |      |     |  |

|------------------------------------|------------------------------------|---------------------------------------------------|------|-------------|------|-----|--|

| Parameter                          | Symbol Conditions                  |                                                   | min  | min typ max |      |     |  |

| Circuit current                    | I <sub>CC</sub> 1                  | During drive                                      | 6    | 10          | 14   | mA  |  |

|                                    | lCC <sup>2</sup>                   | During lock protection                            | 6    | 10          | 14   | mA  |  |

| 6VREG voltage                      | 6VREG                              | I <sub>6</sub> VREG = 5mA                         | 5.80 | 6.0         | 6.15 | V   |  |

| HB voltage                         | V <sub>HB</sub>                    | I <sub>HB</sub> = 5mA                             | 1.05 | 1.22        | 1.35 | V   |  |

| VOVER voltage                      | VVOVER                             | I <sub>VOVER</sub> = 1mA                          | 12.0 | 12.8        | 13.6 | V   |  |

| CPWM-H level voltage               | <sup>∨</sup> CRH                   |                                                   | 4.35 | 4.55        | 4.75 | ٧   |  |

| CPWM-L level voltage               | VCRL                               |                                                   | 1.45 | 1.65        | 1.85 | ٧   |  |

| CPWM oscillation frequency         | FPWM                               | C = 100pF                                         | 18   | 25          | 32   | kHz |  |

| CT pin H level voltage             | V <sub>СТН</sub>                   |                                                   | 3.4  | 3.6         | 3.8  | V   |  |

| CT pin L level voltage             | V <sub>CTL</sub>                   |                                                   | 1.4  | 1.6         | 1.8  | V   |  |

| ICT pin charge current             | I <sub>CT</sub> 1                  | V <sub>CT</sub> = 1.2V                            | 1.6  | 2.0         | 2.5  | μΑ  |  |

| ICT pin discharge current          | I <sub>CT</sub> 2                  | V <sub>CT</sub> = 4.0V                            | 0.16 | 0.20        | 0.28 | μΑ  |  |

| ICT charge/discharge current ratio | RCT                                | I <sub>CT</sub> 1/I <sub>CT</sub> 2               | 8    | 10          | 12   | deg |  |

| OUT-N output voltage               | Von                                | I <sub>O</sub> = 20mA                             | 4    | 10          |      | V   |  |

| OUT-P sink current                 | I <sub>OP</sub>                    |                                                   | 15   | 20          |      | mA  |  |

| Hall input sensitivity             | VHN                                | Zero peak value (including offset and hysteresis) |      | 10          | 20   | mV  |  |

| RD/FG output pin L voltage         | V <sub>RD</sub> /V <sub>FG</sub>   | I <sub>RD</sub> /I <sub>FG</sub> = 5mA            |      | 0.15        | 0.3  | V   |  |

| RD/FG output pin leak current      | I <sub>RDL</sub> /I <sub>FGL</sub> | V <sub>RD</sub> /V <sub>FG</sub> = 16V            |      |             | 30   | μΑ  |  |

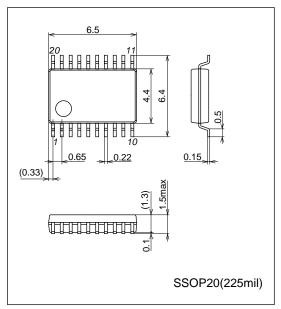

## **Package Dimensions**

unit: mm (typ)

3179C

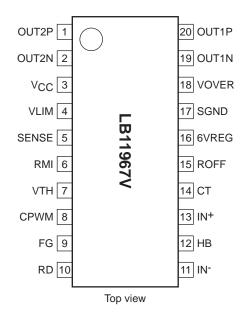

## **Pin Assignment**

#### **Truth Table**

During full-speed rotation

| IN- | IN+ | CT | OUT1P | OUT1N | OUT2P | OUT2N | FG  | RD  | Mode                       |

|-----|-----|----|-------|-------|-------|-------|-----|-----|----------------------------|

| Н   | L   | ,  | L     | L     | OFF   | Н     | L   |     | OUT1 $\rightarrow$ 2 drive |

| L   | Н   | L  | OFF   | Н     | L     | L     | OFF | _   | OUT2 → 1 drive             |

| Н   | L   |    | OFF   | L     | OFF   | Н     | L   | OFF | l a als manda ation        |

| L   | Н   | Н  | OFF   | Н     | OFF   | L     | OFF | OFF | Lock protection            |

| VTH | CPWM | IN- | IN+ | OUT1P | OUT1N | OUT2P | OUT2N                      | Mode                         |

|-----|------|-----|-----|-------|-------|-------|----------------------------|------------------------------|

| L H | Н    | L   | L   | L     | OFF   | Н     | OUT1 $\rightarrow$ 2 drive |                              |

|     | П    | L   | H   | OFF   | Н     | L     | L                          | $OUT2 \rightarrow 1 \ drive$ |

| H L | Н    | L   | OFF | L     | OFF   | Н     | During rotation            |                              |

|     | L    | L   | Н   | OFF   | Н     | OFF   | L                          | Regeneration in lower Tr     |

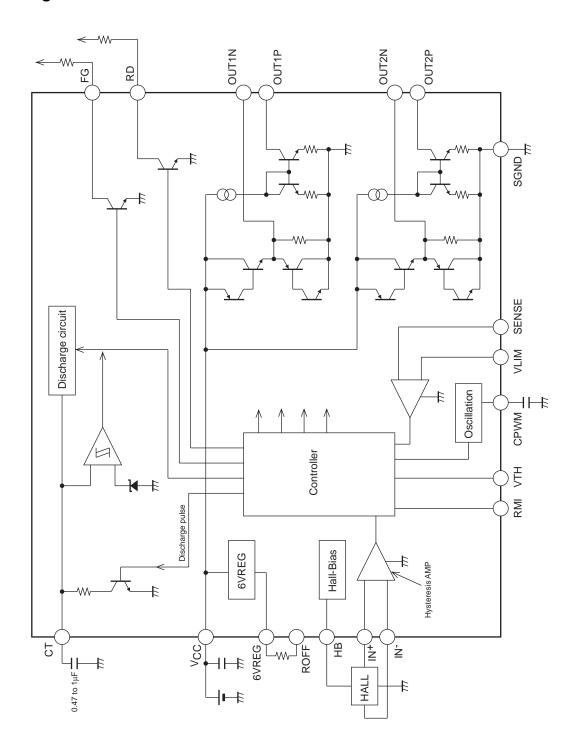

## **Block Diagram**

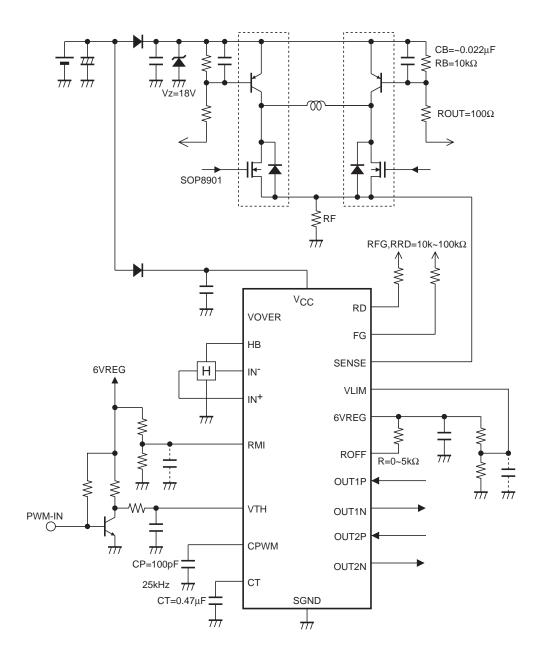

## **Sample Application Circuit 1** (12V)

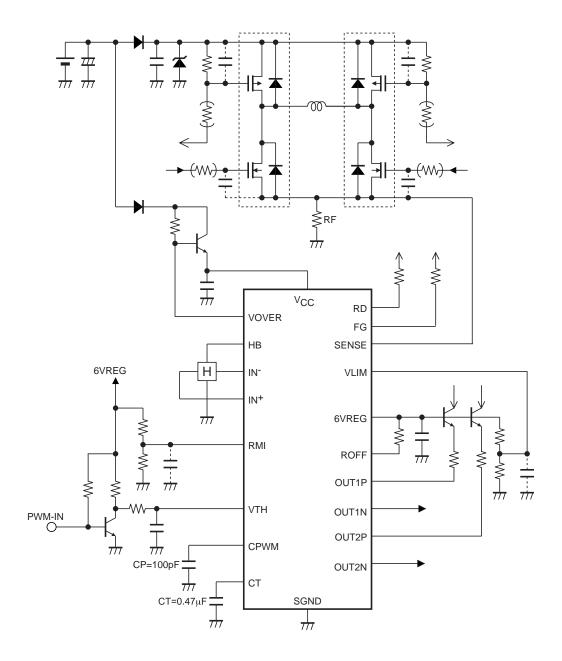

## **Sample Application Circuit 2** (24V, 48V)

#### \*1. < Power supply-GND wiring>

SGND is connected to the control circuit power supply system.

#### \*2. < Power stabilization capacitor for regeneration>

For the CM capacitor that is a power stabilization capacitor for PWM drive and for absorption of kick-back, the capacitance uses  $0.1\mu F$  or more. In this IC, the lower Transistor performs current regeneration by means of switching of upper Transistor. Connect CM between  $V_{CC}$  and GND with the thick pattern and along the shortest route.

#### \*3. <Zener diode to stabilize power supply for regneration>

Be sure to use the zener diode if kick-back causes excessive increase of the supply voltage because such increase damages IC.

#### \*4. <Hall input>

Wiring need to be short to prevent carrying of the noise. If the noise is carried, insert a capacitor between IN+ and IN-. The Hall input circuit is a comparator having a hysteresis of 20mV. It is recommended that the Hall input level is more than three times (60mVp-p) this hysteresis.

#### \*5. < Capacitor to set the PWM oscillation frequency>

With CP = 100pF, oscillation occurs at f = 25kHz and provides the basic frequency of PWM.

#### \*6. <RD output>

This is the open collector output, which outputs "L" during rotation and "H" at stop. This output is left open when not used.

#### \*7. <FG output>

This is the open collector output, which can detect the rotation speed using the FG output according to the phase shift. This output is left open when not used.

#### \*8. <HB pin>

This is a Hall element bias pin, that is, the constant-voltage output pin.

#### \*9. <RMI pin>

This is the minimum speed setting pin, which is pulled up with 6VREG when not used.

When IC power may possibly be turned OFF first when the pin is used, be sure to insert a current limiting resistor to prevent inflow of the large current. (The same applies to the VTH pin.)

#### \*10. <ROFF pin>

This pin sets the soft switching time to cut the reactive current before phase change and is connected to 6VREG when not used.

#### \*11. < VLIM pin>

This pin activates the current limiter when the SENSE pin voltage is higher than the VLIM pin voltage and is connected to 6VREG when not used.

#### \*12. <SENSE pin>

This is connected to GND when not used.

### \*13. <VOVER pin>

This is a pin for constant-voltage bias and should be used for application of 24V and 48V. (Refer to the sample application circuit.) Be sure to use the current limiting resistor. This is left open when not used.

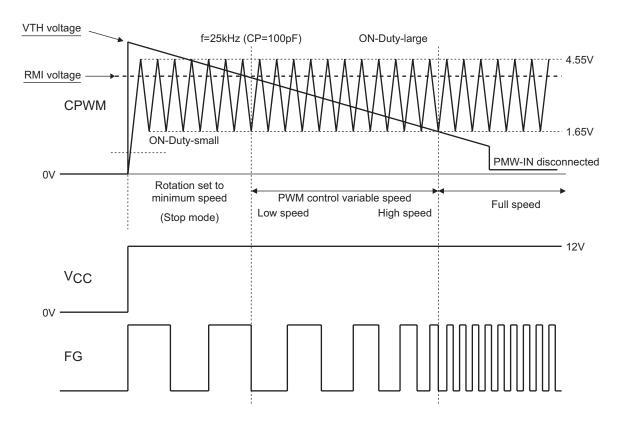

### **Control Timing Chart**

#### (1) Minimum speed setting (stop) mode

PWM-IN input is filtered to generate the VTH voltage. At low speed, the fan rotates with the minimum speed set with RMI pin during low speed. If the minimum speed is not set (RMI = 6VREG), the fan stops.

#### (2) Low⇔High speed mode

PWM control is made through comparison of oscillation and VTH voltages with CPWM changing between  $1.6V \Leftrightarrow 4.6V$ .

When the VTH voltage is lower, the IC switches to drive mode. When the VTH voltage is higher, the p-channel FET is turned off and coil current is regenerated through the low-side FET. Therefore, as the VTH voltage lowers, the output ON-DUTY increases, increasing the coil current and raising the motor speed.

The rotation speed is fed back by the FG output.

#### (3) Full speed mode

The full-speed mode becomes effective with the VTH voltage of 1.65V or less. (VTH must be equal to GND when the speed control is not to be made.)

#### (4) PWM-IN input disconnection mode

When the PWM-IN input pin is disconnected, VTH becomes 1.65V or les and the output enables full drive at 100%. The fan runs at full speed. (Refer to the sample application circuit.)

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa