# Automotive octal low side driver or quad low side plus quad high side driver

Datasheet - production data

#### **Features**

- AEC-Q100 qualified

- Eight integrated PowerMOS configurable as:

- 8 low side ON-OFF with  $R_{ON(max)}$  = 0.3 Ω @  $T_i$  = 175 °C

- High/low side PWM with  $R_{ON(max)}$  = 0.6 Ω @  $T_j$  = 175 °C and 4 Low side with  $R_{ON(max)}$  = 0.3 Ω @  $T_j$  = 175 °C

- Operating battery supply voltage 5 V to 18 V

- Operating V<sub>dd</sub> supply voltage 4.75 V to 5.25 V

- Logic inputs TTL/CMOS-compatible

- Output voltage clamping 37 V typ. in low-side configuration

- SPI interface for outputs control and for diagnosis data communication

- Additional PWM inputs for 8 outputs

- Over temperature protection

- Open load, short to GND, short to VB

- Overcurrent diagnostics in latched or unlatched mode for each channel

- Controlled SR for improved EMC behavior

#### **Description**

The L9301 is a SPI (Serial Peripheral Interface) controlled octal channel with 4 high/low and 4 low side drivers with the possibility to use four integrated PowerMOS as recirculation diodes for PWM load driving.

L9301 contains 12 PowerMOS: 4 configurable High/Low side drivers with  $R_{onmax}$  = 0.6  $\Omega$  (DRN1-4, SRC1-4), 4 low side drivers with  $R_{onmax}$  = 0.6  $\Omega$  (OUT1-4) and 4 low side drivers with  $R_{onmax}$  = 0.3  $\Omega$  (OUT5-8).

The power DRN/SRC1-4 and OUT1-4 can be connected in parallel outside the device in order to get 4 low-side drivers with  $R_{onmax}$  = 0.3  $\Omega$ : DRN1//DRN2, DRN3//DRN4, OUT1//OUT2, OUT3//OUT4.

In this way there is a total of 8 LS channels for ON-OFF mode with  $R_{onmax}$  = 0.3  $\Omega$ .

There is also the possibility to connect the OUT1-4 and OUT5-8 in order to drive in PWM mode a load connected to VB or GND without the necessity of a freewheeling diode. In this case the  $R_{onmax}$  = 0.6  $\Omega$ .

The above configuration can be driven by parallel input or SPI command.

Through the SPI it is possible to configure the device parameters like configuration, Slew-rate, Overcurrent threshold, to send the drivers commands and to read back the diagnosis results.

Table 1. Device summary

| Order code | Package    | Packing     |

|------------|------------|-------------|

| L9301-TR   | PowerSSO36 | Tape & Reel |

Contents L9301

# **Contents**

| 1 | Bloc | ck diagram                                                      |

|---|------|-----------------------------------------------------------------|

| 2 | Pin  | description                                                     |

| 3 | Elec | trical specifications                                           |

|   | 3.1  | Absolute maximum ratings 9                                      |

|   | 3.2  | ESD protection                                                  |

|   | 3.3  | Operating range                                                 |

|   | 3.4  | Thermal data                                                    |

| 4 | Sup  | ply pins                                                        |

|   | 4.1  | VDD 1                                                           |

|   | 4.2  | VB                                                              |

|   | 4.3  | VDD_IO                                                          |

| 5 | Disc | crete inputs1                                                   |

|   | 5.1  | Output enable EN                                                |

|   | 5.2  | Output enable input IN1 to IN8                                  |

|   | 5.3  | Reset input                                                     |

| 6 | Con  | figuration                                                      |

| 7 | Con  | figuration 1: 8 low side drivers16                              |

|   | 7.1  | Configuration 2: 4 low-side PWM mode and 4 low-side drivers     |

|   | 7.2  | Configuration 3: 4 high-side PWM mode and 4 low-side drivers 18 |

|   | 7.3  | Configuration 4: 4 configurable drivers and 8 low-side drivers  |

| 8 | Con  | figurable high/low side driver                                  |

|   | 8.1  | Electrical characteristics DRN/SRC1-4                           |

|   | 8.2  | Driver diagnostic                                               |

|   |      | 8.2.1 Thermal protection                                        |

|   |      | 8.2.2 Overcurrent protection                                    |

|   |      | 8.2.3 Output status                                             |

L9301 Contents

|    |       | 8.2.4     | Charge Pump (CP)                                | . 22 |

|----|-------|-----------|-------------------------------------------------|------|

|    |       | 8.2.5     | DLOSS                                           | . 23 |

|    |       | 8.2.6     | OFF state diagnostic                            | . 23 |

|    |       | 8.2.7     | Over current (OC) comparator self-test          | . 25 |

|    |       | 8.2.8     | Electrical characteristics related to diagnosis | . 25 |

| 9  | Low   | side dri  | ver                                             | 27   |

|    | 9.1   | Electric  | al characteristics OUT1-4                       | 27   |

|    | 9.2   | Electric  | al characteristics OUT5-8                       | 28   |

|    | 9.3   | Driver of | diagnostic                                      | 29   |

|    |       | 9.3.1     | Thermal protection                              | . 29 |

|    |       | 9.3.2     | Overcurrent protection                          | . 29 |

|    |       | 9.3.3     | Output status                                   | . 29 |

|    |       | 9.3.4     | OFF state diagnostic                            | . 30 |

|    |       | 9.3.5     | DLOSS                                           | . 30 |

|    |       | 9.3.6     | OC comparator self-test                         | . 31 |

|    |       | 9.3.7     | Electrical characteristics related to diagnosis | . 31 |

| 10 | Coml  | bined d   | iagnosis (configuration 1, 2 & 3)               | 33   |

| 11 | BIST  |           |                                                 | 34   |

| 12 | Clock | k monit   | or                                              | 35   |

| 40 | ODI   |           |                                                 | 00   |

| 13 |       |           |                                                 |      |

|    | 13.1  | -         | CK, MOSI                                        |      |

|    | 13.2  |           |                                                 |      |

|    | 13.3  | SPI fra   | me                                              | 38   |

|    | 13.4  | SPI reg   | jisters                                         | 39   |

|    | 13.5  | SPI tim   | ings                                            | 45   |

| 14 | Pack  | age info  | ormation                                        | 46   |

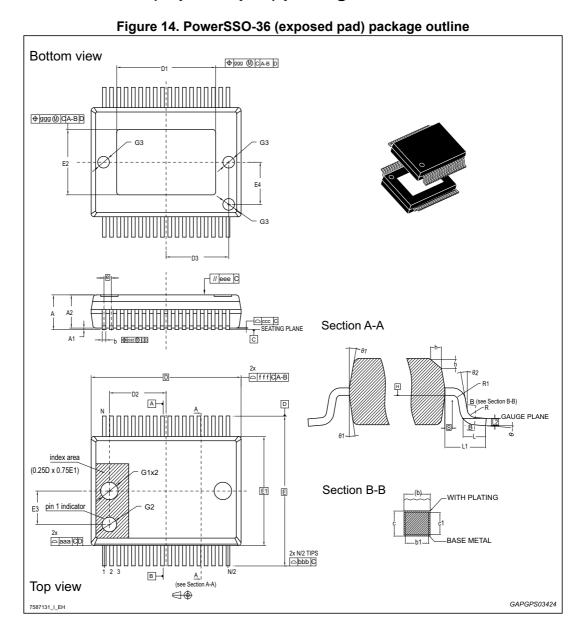

|    | 14.1  | Powers    | SSO-36 (exposed pad) package information        | 46   |

|    | 14.2  | Powers    | SSO-36 (exp. pad) marking information           | 49   |

| 15 | Revis | sion his  | tory                                            | 50   |

|    |       |           |                                                 |      |

List of tables L9301

# List of tables

| Table 1.  | Device summary                                                    | . 1 |

|-----------|-------------------------------------------------------------------|-----|

| Table 2.  | Pin description                                                   | . 7 |

| Table 3.  | Absolute maximum ratings                                          | . 9 |

| Table 4.  | ESD protection                                                    | . 9 |

| Table 5.  | Operating range                                                   | 10  |

| Table 6.  | Thermal data                                                      | 10  |

| Table 7.  | Thermal resistance                                                | 10  |

| Table 8.  | VDD                                                               | 11  |

| Table 9.  | VB                                                                | 12  |

| Table 10. | Output enable input IN1 to IN8                                    | 13  |

| Table 11. | Electrical characteristic of EN, IN18, RES pin                    | 14  |

| Table 12. | Configuration                                                     | 15  |

| Table 13. | Configurable high/low side drivers 1-4 electrical characteristics | 20  |

| Table 14. | Charge pump                                                       | 23  |

| Table 15. | LS diagnostic                                                     | 24  |

| Table 16. | HS diagnostic                                                     | 24  |

| Table 17. | Electrical characteristics related to diagnosis                   | 25  |

| Table 18. | Low-side drivers OUT1-4 electrical characteristics                | 27  |

| Table 19. | Low-side drivers OUT5-8 electrical characteristics                | 28  |

| Table 20. | LS diagnostic                                                     | 30  |

| Table 21. | Electrical characteristics related to diagnosis                   | 31  |

| Table 22. | Configuration 2                                                   |     |

| Table 23. | Configuration 3                                                   | 33  |

| Table 24. | Clock monitor                                                     | 35  |

| Table 25. | CS, SCK, MOSI                                                     | 36  |

| Table 26. | MISO                                                              | 37  |

| Table 27. | SPI timing characteristics                                        | 45  |

| Table 28. | PowerSSO-36 (exposed pad) package mechanical data                 | 47  |

| Table 29. | Document revision history                                         | 50  |

L9301 List of figures

# List of figures

| Figure 1.  | Block diagram                                                                     | 6    |

|------------|-----------------------------------------------------------------------------------|------|

| Figure 2.  | Pin connection diagram                                                            | 7    |

| Figure 3.  | Device assembled on 2s2p PCB with high density vias in contact with a metal plate | . 10 |

| Figure 4.  | Configuration 1: 8 Low side drivers                                               | . 16 |

| Figure 5.  | Configuration 2: 4 low-side PWM mode and 4 low-side drivers                       | . 17 |

| Figure 6.  | Configuration 3: 4 high-side PWM mode and 4 low-side drivers                      | . 18 |

| Figure 7.  | Configuration 4: 4 configurable drivers and 8 low-side drivers                    | . 19 |

| Figure 8.  | Configurable high/low side driver diagram                                         | . 20 |

| Figure 9.  | LS configuration diagnostic                                                       | . 23 |

| Figure 10. | HS configuration diagnostic                                                       | . 24 |

| Figure 11. | Low side driver diagram                                                           |      |

| Figure 12. | LS configuration diagnostic                                                       | . 30 |

| Figure 13. | SPI timing diagram                                                                | . 45 |

| Figure 14. | PowerSSO-36 (exposed pad) package outline                                         | . 46 |

| Figure 15. | PowerSSO-36 (exp. pad) marking information                                        | . 49 |

|            |                                                                                   |      |

Block diagram L9301

# 1 Block diagram

L9301 3.3V low dop Internal regulator Vbg 4 x config . HS/LS drivers VDD VB and VDD 5 chip\_enb monitoring 0.6Ω, 3A, 40V DRN1 Diag DRN2 & Ctrl DRN3 S\_CHK DRN4 Charge pump CP SRC1 SRC2 SRC3 SRC4 IN2 IN3 4 x LS drivers IN4 Logic 0.6Ω. 3A. 40V IN5 → OUT1

→ OUT2

→ OUT3

→ OUT4 Diag S\_CHK IN7 Ctrl IN8 RES 4 x LS drivers 0,3Ω, 3A, 40V EN CLP → OUT5

→ OUT6

→ OUT7

OUT8 SPI SCK S\_CHK SPI CLN MOSI & Ctrl SPI MISO S\_CHK VDD\_I/O Oscillator Safety Vbg2 GND1 Voltage control

Figure 1. Block diagram

GAPG2808151033PS

L9301 Pin description

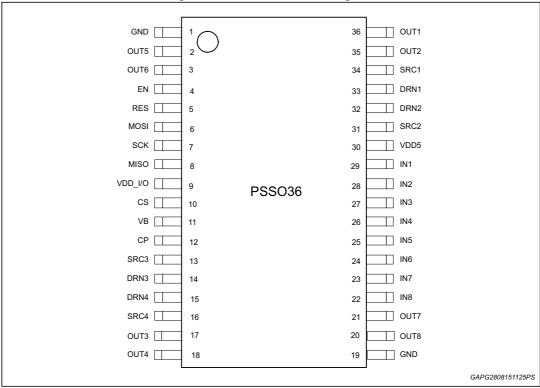

# 2 Pin description

Figure 2. Pin connection diagram

Table 2. Pin description

| Pin | Symbol  | Function                                |

|-----|---------|-----------------------------------------|

| 1   | GND     | Power ground of OUT1,2,5,6              |

| 2   | OUT5    | Output 5                                |

| 3   | OUT6    | Output 6                                |

| 4   | EN      | Enable                                  |

| 5   | RES     | Reset input (active low)                |

| 6   | MOSI    | SPI data in                             |

| 7   | SCK     | SPI serial clock input                  |

| 8   | MISO    | SPI data out                            |

| 9   | VDD_I/O | Microcontroller logic interface voltage |

| 10  | CS      | SPI chip select (active low)            |

| 11  | VB      | Battery supply voltage                  |

| 12  | СР      | Charge pump                             |

| 13  | SRC3    | Source pin of configurable driver #3    |

| 14  | DRN3    | Drain pin of configurable driver #3     |

Pin description L9301

Table 2. Pin description (continued)

| Pin | Symbol | Function                                    |

|-----|--------|---------------------------------------------|

| 15  | DRN4   | Drain pin of configurable driver #4         |

| 16  | SRC4   | Source pin of configurable driver #4        |

| 17  | OUT3   | Output 3                                    |

| 18  | OUT4   | Output 4                                    |

| 19  | GND    | Power ground of OUT3,4,7,8                  |

| 20  | OUT8   | Output 8                                    |

| 21  | OUT7   | Output 7                                    |

| 22  | IN8    | Discrete input used to PWM output driver #8 |

| 23  | IN7    | Discrete input used to PWM output driver #7 |

| 24  | IN6    | Discrete input used to PWM output driver #6 |

| 25  | IN5    | Discrete input used to PWM output driver #5 |

| 26  | IN4    | Discrete input used to PWM output driver #4 |

| 27  | IN3    | Discrete input used to PWM output driver #3 |

| 28  | IN2    | Discrete input used to PWM output driver #2 |

| 29  | IN1    | Discrete input used to PWM output driver #1 |

| 30  | VDD5   | 5 Volt supply input                         |

| 31  | SRC2   | Source pin of configurable driver #2        |

| 32  | DRN2   | Drain pin of configurable driver #2         |

| 33  | DRN1   | Drain pin of configurable driver #1         |

| 34  | SRC1   | Source pin of configurable driver #1        |

| 35  | OUT2   | Output 2                                    |

| 36  | OUT1   | Output 1                                    |

| EP  | GND    | Exposed pad: connected to GND               |

DocID028688 Rev 6

# 3 Electrical specifications

### 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol                                                                                                                                     | Parameter                        | Value [DC voltage]         | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|------|

| VB                                                                                                                                         | Supply voltage                   | -0.3 to 35                 | V    |

| VDD, VDD_I/O                                                                                                                               | Stabilized supply voltage        | -0.3 to 18( <sup>(1)</sup> | V    |

| V <sub>CS</sub> , V <sub>SCK</sub> , V <sub>MOSI</sub> ,<br>V <sub>MISO</sub> , V <sub>EN</sub> , V <sub>IN1-8</sub> ,<br>V <sub>RES</sub> | Logic input/output voltage range | -0.3 to 18 <sup>(1)</sup>  | ٧    |

| OUT1-8                                                                                                                                     | -                                | -1 to VCL                  | V    |

| SRC1-4                                                                                                                                     | -                                | -1 to VB                   | V    |

| DRN1-4                                                                                                                                     | -                                | -1 to VCL                  | V    |

| СР                                                                                                                                         | -                                | -0.3 to (VB+CP_DELTA)      | V    |

| GND                                                                                                                                        | -                                | -0.3 to +0.3               | V    |

<sup>1.</sup> Short to 18 V for 100 h max.

Note:

A suitable device to clamp the voltage during 'load dump' event to a value ≤35 V must be present at application level.

# 3.2 ESD protection

Table 4. ESD protection

| Parameter                                                                                      | Value | Unit |

|------------------------------------------------------------------------------------------------|-------|------|

| ESD according to Human Body Model (HBM), Q100-002 for pins $^{(1)}\!;$ (100 pF/1.5 k $\Omega)$ | ±4000 | V    |

| ESD according to Human Body Model (HBM), Q100-002 for all other pins; (100 pF/1.5 k $\Omega$ ) | ±2000 | V    |

| ESD according to Charged Device Model (CDM), Q100- 011 Corner pins                             | ±750  | V    |

| ESD according to Charged Device Model (CDM), Q100-011 Non-corner pins                          | ±500  | V    |

<sup>1.</sup> VB, DRN1-4, SRC1-4, OUT1-8.

# 3.3 Operating range

**Table 5. Operating range**

| Symbol | Parameter                   | Min.   | Max.   | Unit |

|--------|-----------------------------|--------|--------|------|

| VB     | Supply voltage              | VB_UV  | 18     | V    |

| VDD    | Stabilized supply voltage   | VDD_UV | VDD_OV | V    |

| VDD_IO | Logic output supply voltage | 3.0    | 5.5    | V    |

#### 3.4 Thermal data

Table 6. Thermal data

| Symbol                          | Parameter                               | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------------------------|------|------|------|------|

| T <sub>amb</sub> <sup>(1)</sup> | Operating ambient temperature           | -40  | -    | 125  | °C   |

| T <sub>stg</sub>                | Storage temperature                     | -40  | -    | 150  | °C   |

| T <sub>j</sub>                  | Junction temperature                    | -40  | -    | 175  | °C   |

| T <sub>sd</sub>                 | Thermal shutdown temperature            | 180  | -    | 195  | °C   |

| T <sub>sd-hys</sub>             | Thermal shutdown temperature hysteresis | -    | 10   | -    | °C   |

<sup>1.</sup> For information only, in any case  $T_i$  limits must not exceed.

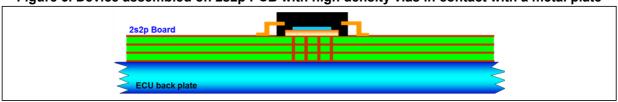

Table 7. Thermal resistance

| Symbol                        | Parameter                | Working conditions                                 | Value | Unit |

|-------------------------------|--------------------------|----------------------------------------------------|-------|------|

| R <sub>th j-amb</sub>         | Junction to ambient      | 2s2p (4L) board; Natural convection <sup>(1)</sup> | 27    | °C/W |

|                               | Junction to ambient      | 2s2p (4L) board on ECU metal plate <sup>(2)</sup>  | 8     | °C/W |

| R <sub>th j-bottom case</sub> | Junction to bottom case  | Bottom cold plate <sup>(3)</sup>                   | 1     | °C/W |

| R <sub>th j-top case</sub>    | Junction to top case     | Top cold plate <sup>(4)</sup>                      | 21    | °C/W |

| Psi <sub>j-top case</sub>     | Psi Junction to top case | 2s2p (4L) board; Natural convection (1)            | 2     | °C/W |

- 1. Jedec STD. JESD51.

- 2. Package assembled on 2s2p (4L) board. The board bottom side is in contact with a metal plate as per typical automotive application (ECU system). See *Figure 3*.

- Thermal resistance between the die and the bottom case surface in ideal contact and measured by cold plate as per Jedec best practice guidelines (JESD51).

- 4. Thermal resistance between the die and the top case surface in ideal contact and measured by cold plate as per Jedec best practice guidelines (JESD51).

Figure 3. Device assembled on 2s2p PCB with high density vias in contact with a metal plate

10/51 DocID028688 Rev 6

L9301 Supply pins

## 4 Supply pins

#### 4.1 VDD

An external  $\pm 5.0 \pm 0.25$  VDC supply provided from an external source is the primary power source to the L9301. This supply is used as the power source for all of its internal logic circuitry and other miscellaneous functions.

The VDD is monitored for under and over voltage and a dedicated SPI flag of each event is set to report those conditions. The device behavior in case of VDD fault detection can be defined using the proper configuration bit that allows to choose if the OUT must be disabled or not.

| _ |     |             |                                                 |                |      |      |      |      |

|---|-----|-------------|-------------------------------------------------|----------------|------|------|------|------|

|   | Pin | Symbol      | Parameter                                       | Test condition | Min. | Тур. | Max. | Unit |

| Ī |     | VDD_UV      | VDD undervoltage detection threshold            | VDD decreasing | 4.5  | -    | 4.7  | V    |

|   | VDD | VDD_uv_filt | VDD undervoltage filter time for output disable | Tested by scan | 90   | -    | 145  | μs   |

|   | VDD | VDD_OV      | VDD overvoltage detection threshold             | VDD increasing | 5.25 | -    | 5.5  | V    |

|   |     | VDD_ov_filt | VDD overvoltage filter time for output disable  | Tested by scan | 90   | -    | 145  | μs   |

Table 8, VDD

#### 4.2 VB

This input is the supply for the on board charge pump and it shall be connected to protected battery line. In case of high-side configuration, to get the specified Ron value this pin must be connected to the same VB where the loads are connected. If it is present an additional voltage drop between the two VB, the  $R_{dson}$  of that given output will be higher than the specified maximum.

The VB is monitored for under and over voltage and a dedicated SPI flag of each event is set to report those conditions. The device behavior in case of VB fault detection can be defined using the proper configuration bit that allows to choose if the OUT must be disabled or not.

Supply pins L9301

Table 9. VB

| Pin          | Symbol     | Parameter                           | Test condition | Min. | Тур. | Max. | Unit |

|--------------|------------|-------------------------------------|----------------|------|------|------|------|

|              | VB_UV      | VB undervoltage detection threshold | VB decreasing  | 3.5  | -    | 4    | V    |

|              | VB_UV_on   | VB undervoltage detection threshold | VB increasing  | 4    | -    | 4.5  | V    |

|              | VB_UV_hys  | VB undervoltage hysteresis          | -              | 0.1  | -    | 1    | V    |

| \ \rac{1}{2} | VB_UV_filt | VB undervoltage filtering time      | Tested by scan | 90   | -    | 145  | us   |

| VB           | VB_OV      | VB overvoltage detection threshold  | VB increasing  | 19   | -    | 22   | V    |

|              | VB_OV_on   | VB overvoltage detection threshold  | VB decreasing  | 19   | -    | 21   | V    |

|              | VB_UV_hys  | VB overvoltage hysteresis           | -              | 0.1  | -    | 1    | V    |

|              | VB_OV_filt | VB overvoltage filtering time       | Tested by scan | 90   | -    | 145  | μs   |

# 4.3 VDD\_IO

This pin is used to supply the discrete MISO output stage of L9301 and must be connected to the same voltage used to supply the peripherals of the processor interfaced to L9301.

L9301 Discrete inputs

### 5 Discrete inputs

#### 5.1 Output enable EN

The EN pin is the general output enable which allows the  $\mu$ C to immediately switch off the output in case of need. Output driving is allowed only if this pin is driven to high level. The device configuration can be changed only with EN pin driven to low level.

An internal pull down is present on the pin.

### 5.2 Output enable input IN1 to IN8

These inputs allow the outputs, depending on the configuration selected, to be enabled without the use of the SPI. The SPI command and the IN1-8 input are logically OR'd together.

A logic '1' on this input will enable the correspondent output no matter what the status of the SPI command register is. A logic '0' on this input will disable this output if the SPI command register is not commanding this output on. These pins can be left 'open' if the internal power stages are controlled only via the SPI. This input has a nominal 100 k $\Omega$  pull down resistor to GND, which will pull this pin to ground if an open circuit condition occurs. This input is ideally suited for loads that are pulse width modulated (PWM'd). This allows PWM control without the use of the SPI inputs.

OUTx/DRNx/SRCx ΕN **RESET INx** Χ 0 Χ **OFF** 0 Χ OFF Χ 1 1 0 **OFF** 1 1 1 ON

Table 10. Output enable input IN1 to IN8

Discrete inputs L9301

## 5.3 Reset input

When this input goes low it resets all the internal registers and switches off all the output stages. This input has a nominal 100 k $\Omega$  resistor connected from this pin to the internal 3.3 V regulator, which will pull this pin to 3.3 V if an open circuit condition occurs.

Table 11. Electrical characteristic of EN, IN1...8, RES pin

| Pin                 | Symbol | Parameter                | Test condition                                         | Min. | Тур. | Max.    | Unit |

|---------------------|--------|--------------------------|--------------------------------------------------------|------|------|---------|------|

|                     | V_IH   | Logic input high voltage | -                                                      | 1.75 |      | VDD+0.3 | V    |

| IN18,<br>EN,<br>RES | V_IL   | Logic input low voltage  | -                                                      | -0.3 |      | 0.75    | V    |

|                     | V_Ihys | Logic input hysteresis   | -                                                      | 100  |      | 1000    | mV   |

| IN18, EN            | Ri_pd  | Pull down resistor       | Tested at 1.5 V                                        | 50   | 100  | 150     | kΩ   |

| RES                 | Ri_pu  | Pull up resistor         | Tested at 1.5 V,<br>R = (3.3-1.5)/I <sub>measure</sub> | 50   | 100  | 150     | kΩ   |

L9301 Configuration

# 6 Configuration

The selected configuration can be configured by SPI, there are 2 bits dedicated to configuration selection:

**Table 12. Configuration**

| Bit1 | Bit0      | Configuration | Input → Output                                                                             | Description                                                                                                                                                                         |

|------|-----------|---------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0         |               |                                                                                            | 8 low side channels with $R_{dson} = 0.3 \Omega$                                                                                                                                    |

|      |           |               | IN5-8 → OUT5-8                                                                             | 2001                                                                                                                                                                                |

| 0    | 1         | 2             | IN1-4 $\rightarrow$ OUT1-4<br>IN5-8 $\rightarrow$ OUT5-8                                   | 4 low side channels with $R_{dson}$ = 0.6 $\Omega$<br>4 low side channels with $R_{dson}$ = 0.3 $\Omega$                                                                            |

| 1    | 0         | 3             | IN1-4 → SRC1-4,<br>IN5-8 → OUT5-8                                                          | 4 high side channels with $R_{dson}$ = 0.6 $\Omega$<br>4 low side channels with $R_{dson}$ = 0.3 $\Omega$                                                                           |

| 1    | 1 1 4 IN5 |               | IN1-4 $\rightarrow$ OUT1-4,<br>IN5-8 $\rightarrow$ OUT5-8,<br>SPI $\rightarrow$ DRN/SRC1-4 | 4 low side channels with R <sub>dson</sub> = 0.6 $\Omega$<br>4 low side channels with R <sub>dson</sub> = 0.3 $\Omega$<br>4 low/high side ch. with R <sub>dson</sub> = 0.6 $\Omega$ |

The configuration is enabled only when EN pin is logic 0.

In configuration 4, the output DRN/SRC1-4 can be controlled by SPI only; for those outputs the selection between high side and low side configuration can be done through the dedicated bit (bit8 of Device general configuration register).

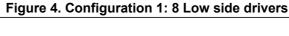

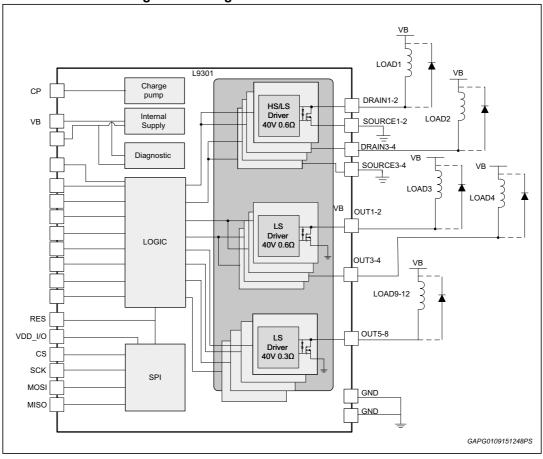

#### Configuration 1: 8 low side drivers 7

In this configuration there are 8 low side drivers available that can be driven by SPI or by the parallel input: IN1-4 control both DRAIN1-4 and OUT1-4 that must be turned on and off simultaneously while IN5-8 control OUT5-8.

The corresponding relations are:

- IN1: OUT1 & OUT2;

- IN2: OUT3 & OUT4;

- IN3: DRN1 & DRN2;

- IN4: DRN3 & DRN4

#### 7.1 Configuration 2: 4 low-side PWM mode and 4 low-side drivers

In this configuration there are 4 low side drivers with integrated free-wheeling diodes and 4 low side drivers available. All the channels can be driven by SPI or by the parallel input. To enable the OUT1-4 driving, the PWM enable SPI bit for OUT1-4 and SRC1-4 must be set.

The IN1-4 control the low side power OUT1-4 used to drive the LOAD1-4 and the device should assure that when the low-side is switched off, the high-side, acting as a free-wheeling diode, must be turned on. To avoid cross conduction the LS VGS voltage is monitored.

When OUT1-4 are commanded ON either by INx or SPI, the L9301 switches off the HS first, then with 2 µs delay after detecting HS VGS low, it switches on LS.

When OUT1-4 are commanded OFF either by INx or SPI, the L9301 switches off the LS first, then with 2 µs delay after detecting LS VGS low, it switches on the HS.

#### IN5-8 control OUT5-8

The selected configuration must be configured by SPI.

The corresponding relations are:

- IN1: OUT1 ↔ SRC2:

- IN2: OUT2 ↔ SRC1:

- IN3: OUT3 ↔ SRC4;

- IN4: OUT4 ↔ SRC3

L9301 ) I OAD 1- 4 Charge СР DRN1-4 HS/LS Internal VB SRC1-4 40V 0.6Ω V5\ ΕN OUT1-4 IN2 LS IN3 Driver 40V 0.6Ω IN4 VΒ LOGIC IN5 IN6 LOAD 5-8 IN7 IN8 OUT5-8 LS Driver 40V 0.3Ω VDD I/C CS SCK SPI MOS GAPG0109151552PS

Figure 5. Configuration 2: 4 low-side PWM mode and 4 low-side drivers

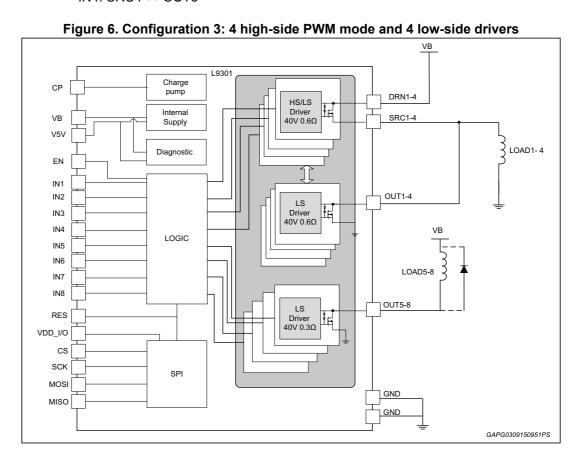

# 7.2 Configuration 3: 4 high-side PWM mode and 4 low-side drivers

In this configuration there are 4 high side drivers with integrated free-wheeling diodes and 4 low side drivers available. All the channels can be driven by SPI or by the parallel input. To enable the SRC1-4 driving, the PWM enable SPI bit for SRC1-4 and OUT1-4 must be set.

The IN1-4 control the high side power SRC1-4 used to drive the LOAD1-4 and the device should assure that when the high-side is switched off, the low-side, acting as a free-wheeling diode, must be turned on. To avoid cross conduction the HS VGS voltage is monitored.

When SRC1-4 is commanded ON either by INx or SPI, the L9301 switches off the HS first, then with 2  $\mu$ s delay after detecting HS VGS low, it switches on LS.

When SRC1-4 is commanded OFF either by INx or SPI, the L9301 switches off the HS first, then with 2 µs delay after detecting HS VGS low, it switches on the LS.

#### IN5-8 control OUT5-8

The selected configuration must be configured by SPI.

Note: The corresponding relations are:

- IN1: SRC1 ↔ OUT2;

- IN2: SRC2 ↔ OUT1;

- IN3: SRC3 ↔ OUT4;

- IN4: SRC4 ↔ OUT3

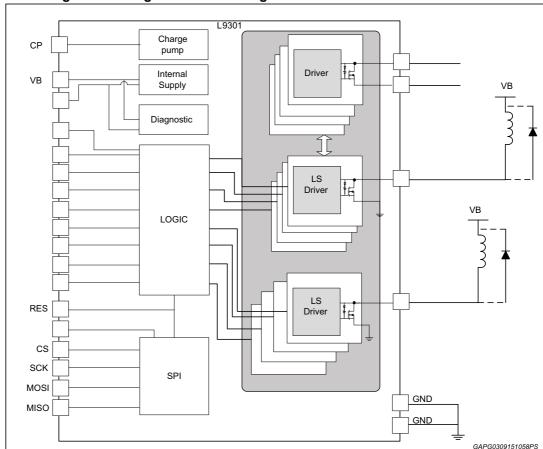

# 7.3 Configuration 4: 4 configurable drivers and 8 low-side drivers

In this configuration there are 4 HS/LS drivers and 8 low side drivers available. All the LS can be driven by SPI or by the parallel input.

The IN1-8 control OUT1-8 while the configurable driver can only be controlled by SPI.

The four configurable drivers (DRN1-4, SRC1-4) can be configured separately as LS or HS using the dedicated SPI bit.

Figure 7. Configuration 4: 4 configurable drivers and 8 low-side drivers

# 8 Configurable high/low side driver

The channels 1 to 4 can be configured as high or low side. In the low side configuration an internal clamp is present.

In high side configuration, the DRNx are connected to VB pin in PCB. To guarantee the OC (over current) function, the DRNx voltage is within the range of (VB-1 V, VB+1 V).

Figure 8. Configurable high/low side driver diagram

#### 8.1 Electrical characteristics DRN/SRC1-4

5 V  $\leq$  VB < 18 V;  $-40^{\circ}$ C  $\leq$  T<sub>i</sub>  $\leq$  175 $^{\circ}$ C unless otherwise specified.

Table 13. Configurable high/low side drivers 1-4 electrical characteristics

| Pin    | Symbol                 | Parameter | Test condition            | Min. | Тур. | Max. | Unit |

|--------|------------------------|-----------|---------------------------|------|------|------|------|

| DRN1-4 | Res                    | _         | HS/LS configuration       | _    | _    | 0.6  | Ω    |

| SRC1-4 | R <sub>DS-on_HLS</sub> |           | VB = 13.5 V; I_load = 1 A |      |      | 0.0  | 32   |

20/51 DocID028688 Rev 6

Table 13. Configurable high/low side drivers 1-4 electrical characteristics (continued)

| Pin              | Symbol                    | Parameter                              | Test condition                                                                          | Min. | Тур. | Max. | Unit |

|------------------|---------------------------|----------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

|                  |                           | Output leakage current                 | HS configuration<br>DRNx = 13.5 V; SRCx = 0 V                                           | -    | -    | 10   | μΑ   |

|                  | IOUT_LK_HLS               | Output leakage current                 | LS configuration<br>DRNx = 13.5 V; SRCx = 0 V                                           | -    | -    | 10   | μΑ   |

|                  |                           | Voltage S/R on/off                     | HS/LS configuration<br>VB 13.5 V<br>Load: 8 Ω, 10 nF – From 80%<br>to 30% of DRNx(SRCx) | 2    | 4    | 6    | V/µs |

|                  | Vs/R_HLS                  |                                        | HS/LS configuration VB 13.5 V Load: 8 Ω, 10 nF – From 80% to 30% of DRNx(SRCx)          | 5    | 10   | 15   | V/µs |

|                  | T <sub>turn-on_HLS</sub>  | Turn-on delay time                     | HS configuration<br>VB 13.5 V<br>From command to 10% SRCx<br>Load: 8 Ω, 10 nF           | -    | -    | 3    | μs   |

| DRN1-4<br>SRC1-4 |                           |                                        | LS configuration<br>VB 13.5 V<br>From command to 90% DRNx<br>Load: 8 Ω, 1 0nF           | -    | -    | 3    | μs   |

| 3801-4           | T <sub>turn-off_HLS</sub> | Turn-off delay time                    | HS configuration<br>VB 13.5 V<br>From command to 90% SRCx<br>Load: 8 Ω, 10 nF           | -    | -    | 3    | μs   |

|                  |                           |                                        | LS configuration<br>VB 13.5 V<br>From command to 10% DRNx<br>Load: 8 Ω, 10 nF           | -    | -    | 3    | μs   |

|                  |                           | Output clamping                        | LS configuration<br>I_load= 0.6 A T = 130 °C                                            | 34   | 37.5 | 41   |      |

|                  | V <sub>CL_LS</sub>        | Output clamping voltage                | LS configuration<br>I_load = 0.6 A, T = -40 °C and<br>25 °C                             | 35   | 37.5 | 41   | V    |

|                  | E <sub>clampSP_LS</sub>   | Clamp repetitive pulse energy ATE test | LS configuration<br>I_load = 0.7 A, T <sub>j</sub> = 150 °C,<br>100 kpulses             | -    | -    | 5    | mJ   |

|                  | E <sub>clampSP_LS</sub>   | Clamp single pulse energy ATE test     | LS configuration<br>I_load = 0.7 A, T <sub>j</sub> = 150 °C                             | -    | -    | 10   |      |

#### 8.2 Driver diagnostic

#### 8.2.1 Thermal protection

Each solenoid channel has a dedicated temperature sensor that continuously monitors the temperature of the PowerMOS.

In case the shutdown temperature  $T_{sd}$  is reached the related channel is turned off and the dedicated diagnostic bits are set.  $t\_sdl\_x$  is the bit that latches the thermal shut down and it is cleared after sending dedicated SPI to clear the bit,  $t\_sd\_x$  is the other thermal shut down bit and once it is set by thermal shut down condition it is cleared only when the  $T_j$  decreases below the thermal shut down threshold (hysteresis). If the microcontroller, when the device is still in temperature shut down condition ( $t\_sd\_x = 1$ ), clears the  $t\_sdl\_x$  and tries to turn on the output, the actuation is not performed and the  $t\_sdl\_x$  will be set again. To avoid these multiple interrupts the microcontroller can poll the  $t\_sd\_x$  bit and enable the next actuation only when the bit is zero.

To re-switch on the channel after thermal shut down, the SPI needed to switch off the channel is required.

#### 8.2.2 Overcurrent protection

An overcurrent protection is present for each driver DRN/SRC1...4. The overcurrent threshold is selectable through oc\_thres\_x (where x indicates the channel). In case of overcurrent the output driver is turned off, the related SPI command bit is set to 0 and a dedicated diagnostic bit is set oc\_x where x indicates the channel where the fault occurred.

If bit oc\_restart = 0, to restart the channel the microcontroller has to clear the fault bit (reading the fault register), and to write to 1 the SPI command bit or to provide a rising edge on the parallel input command.

If bit oc\_restart = 1, the restart function is activated. The slew rate of the channel in fault condition is automatically set to the higher value to limit dissipation issue then to restart the channel the microcontroller has to write to 1 the SPI command bit or to provide a rising edge on the parallel input command. The diagnostic bit oc\_x can be cleared only by writing it to 0 in the corresponding driver status register by SPI however the channel can be restarted as described above.

#### 8.2.3 Output status

During the ON phase, the output voltage is compared with the VTopen threshold voltage in order to verify if the output status is aligned with the ON command:

- in case of low side usage if the DRNx voltage is above the VTopen threshold a

dedicated bit is set to indicate the anomaly

- in case of high side usage if the SRCx voltage is below the VTopen threshold a dedicated bit is set to indicate the anomaly

#### 8.2.4 Charge Pump (CP)

The charge pump is enabled when the selected configuration includes high side drivers (like configuration 2, 3, 4). In configuration 1 the charge pump is internally shorted to VB.

On the CP pin it's required to connect a 100 nF capacitor toward the VB line.

The charge pump is ON if VB > UV threshold & VDD > UV threshold

22/51 DocID028688 Rev 6

The charge pump is OFF if VB< UV threshold or VDD< UV threshold. The CP voltage is equal to VB-Vbe.

When the CP is ON, the low CP diagnosis is enabled. When any HS is switched on but CP voltage is not high enough to switch on HS, low CP fault is detected. A SPI bit allows configuring the actions to be taken in case of low CP fault.

Table 14. Charge pump

| Pin | Symbol   | Parameter           | Test condition | Min. | Тур. | Max. | Unit |

|-----|----------|---------------------|----------------|------|------|------|------|

| CP  | CP_DELTA | Delta voltage CP-VB | VB>5V          | 3    | -    | 6    | V    |

#### 8.2.5 **DLOSS**

When the L9301 is configured with low side and external diodes are used for freewheeling, there is the possibility through a dedicated SPI bit to enable the 'diode loss' diagnosis that is used to detect if the external diode is no more connected checking if during the OFF phase the internal clamp is activated. Another SPI bit allows configuring the actions to be taken in case of DLOSS fault.

When the L9301 is configured as high side and internal/external diodes are used for freewheeling, there is the possibility through a dedicated SPI bit to enable the 'diode loss' diagnosis that is used to detect if the diode is no more connected checking if during the OFF phase the HS is forced to switch on. Another SPI bit allows configuring the actions to be taken in case of DLOSS fault.

In addition, diode loss on LS (including configurable channels configured as LS) is only detected when VBOV is not present.

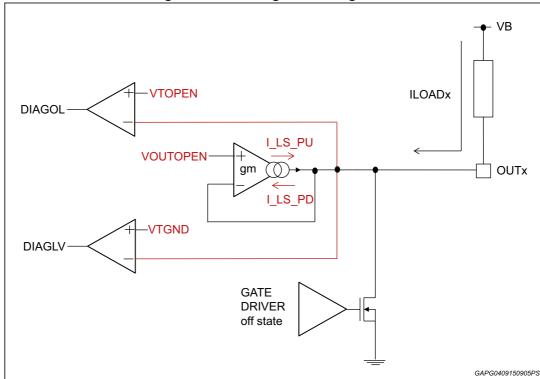

#### 8.2.6 OFF state diagnostic

The device provides the off-state diagnostic for each channel.

In low-side configuration the short to ground and open load faults can be detected. The fault is reported in a SPI register.

Figure 9. LS configuration diagnostic VTOPEN ILOADx DIAGOL I LS PU VOUTOPEN  $\mathcal{O}$ DRNx LISPE TGND DIAGIV GATE DRIVER off state SRCx GAPG0309151526PS

Table 15. LS diagnostic

| DIAGOL | DIAGLV | FAULT DETECTION |  |  |

|--------|--------|-----------------|--|--|

| 0      | 0      | no fault        |  |  |

| 0      | 1      | not possible    |  |  |

| 1      | 0      | open load       |  |  |

| 1      | 1      | short to ground |  |  |

In high-side configuration the short to battery and open load faults can be detected. The fault is reported in a SPI register.

Figure 10. HS configuration diagnostic

GATE

DRIVER

Off state

VOUTOPEN

DIAGOL

VOUTOPEN

JUNE

Table 16. HS diagnostic

| DIAGOL | DIAGLV | FAULT DETECTION |

|--------|--------|-----------------|

| 0      | 0      | short to ground |

| 0      | 1      | not possible    |

| 1      | 0      | open load       |

| 1      | 1      | no fault        |

The diagnostic blanking time is configurable through the dedicated diagoff\_blank\_sel bit.

The OFF diagnosis is triggered at driver OFF CMD and will not be refreshed after clearing the flags. To recover the OFF diagnosis in OFF stage, send SPI to disable OFF diagnosis and then enable it.

#### 8.2.7 Over current (OC) comparator self-test

L9301 provides driver OC (over current) comparator self-test function. During OFF phase, the OC comparator still works and the expected result is '1' due to high drain-source voltage. If L9301 detects OC '0' during OFF phase, the SPI bit oc\_comparator\_f is set to '1'.

For DRN1-4, when they are configured as LS, a Short To Ground (STG) fault will not trigger OC '1', so L9301 will report both STG and OC comparator self-test fail, when they are configured as HS, a short-to-battery (STB) fault will not trigger OC '1', so L9301 will report both STB and OC comparator self-test fail.

#### 8.2.8 Electrical characteristics related to diagnosis

Table 17. Electrical characteristics related to diagnosis

| Pin              | Symbol                                 | Parameter                                            | Test condition   | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------|------------------------------------------------------|------------------|------|------|------|------|

|                  | T <sub>Over_temperature_blanking</sub> | Over temperature blanking time                       | Tested by scan   | 1    | -    | 1.5  | μs   |

|                  | T <sub>Over_temperature_filter</sub>   | Over temperature filter time                         | Tested by scan   | 2    | -    | 5    | μs   |

|                  | T <sub>Charge_pump_low</sub>           | Charge pump low filter time                          | Tested by scan   | 3    | -    | 5    | μs   |

|                  | T <sub>Charge_pump_low_blanking</sub>  | Charge pump low blanking time                        | Tested by scan   | 25   | -    | 40   | μs   |

|                  | T <sub>diode_loss_filter_time</sub>    | Diode loss filter time                               | Tested by scan   | 3    | -    | 5    | μs   |

|                  | R <sub>open_load_HLS</sub>             | Min. resistor value open load detection              | Not tested       | 10   | -    |      | kΩ   |

|                  | I <sub>OC_HLS</sub>                    | Over current threshold 1                             | -                | 1    | 2    | 3    | А    |

| DRN1-4<br>SRC1-4 | I <sub>OC_HLS</sub>                    | Over current threshold 2                             | -                | 3    | 4    | 5    | А    |

| SRC1-4           | T <sub>FLT_OC_HLS</sub>                | Over current filtering time                          | Tested by scan   | 3    | -    | 5    | μs   |

|                  | T <sub>FLT_diagoff_HLS</sub>           | Filtering open load<br>and short to GND<br>diag. off | Tested by scan   | 55   | -    | 80   | μs   |

|                  | T <sub>d_blank0_HLS</sub>              | Diagnosis blanking time after switch-off             | Tested by scan   | 900  | -    | 1300 | μs   |

|                  | T <sub>d_blank1_HLS</sub>              | Diagnosis blanking time after switch-off             | Tested by scan   | 450  | -    | 650  | μs   |

|                  | V <sub>TOPEN_HS</sub>                  | Open load threshold                                  | HS configuration | 1.9  | 2.1  | 2.3  | V    |

|                  | V <sub>TOPEN_LS</sub>                  | voltage                                              | LS configuration | 2.7  | 2.9  | 3.1  | V    |

Table 17. Electrical characteristics related to diagnosis (continued)

| Pin              | Symbol                    | Parameter                                                                 | Test condition                                                     | Min. | Тур. | Max. | Unit |

|------------------|---------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|------|

|                  | V <sub>OUTOPEN_</sub> HLS | Open load output voltage                                                  | HS and LS<br>configuration<br>Open load<br>condition               | 2,3  | -    | 2,7  | V    |

|                  | V <sub>TVBAT_HS</sub>     | Output short-circuit<br>to VB voltage<br>threshold (HS<br>configuration)  | HS configuration                                                   | 2.7  | -    | 3.1  | V    |

|                  | $V_{TGND\_LS}$            | Output short-circuit<br>to GND voltage<br>threshold (LS<br>configuration) | LS configuration                                                   | 1.9  | ı    | 2.3  | >    |

|                  | 1.                        | Output diagnostic pull- down current @                                    | HS configuration<br>DRNx =13.5V<br>SRCx =5V                        | 210  | 245  | 300  | μΑ   |

| DRN1-4<br>SRC1-4 | OFF STATE                 | LS configuration<br>DRNx =5V<br>SRCx =0V                                  | 40                                                                 | 70   | 100  | μΑ   |      |

|                  |                           | Output diagnostic                                                         | HS configuration<br>DRNx =13.5V<br>SRCx =1.5V                      | 40   | 70   | 100  | μΑ   |

|                  | lout_pu_hls               | pull-up current @<br>OFF STATE                                            | LS configuration<br>DRNx =1.5V<br>SRCx =0V                         | 50   | 75   | 100  | μΑ   |

|                  | -                         | Minimum OFF time<br>for correct diagnostic<br>(Blank time 0)              | Application note<br>NOT TESTED<br>(ESD cap < 12nF,<br>Bit_blank=0) | -    | 1380 | -    | μs   |

|                  | -                         | Minimum OFF time<br>for correct diagnostic<br>(Blank time 1)              | Application note<br>NOT TESTED<br>(ESD cap < 6nF,<br>Bit_blank=1)  | -    | 730  | -    | μs   |

L9301 Low side driver

### 9 Low side driver

The channels OUT1 to 8 are low side drivers with internal clamp.

VDD5

3,3V low dropout reg.

Driver

Diagnosis & protection

SPI

CAPGNA091508111PS

Figure 11. Low side driver diagram

#### 9.1 Electrical characteristics OUT1-4

5 V  $\leq$  VB < 18 V; -40 °C  $\leq$  T $_{i}$   $\leq$  175 °C unless otherwise specified.

**Symbol** Unit Pin **Parameter Test condition** Min. Тур. Max. Drain-source I load = 1A0.6 Ω R<sub>DS-on LS</sub> resistance Output leakage OUTx = 13.5 V 10 μΑ I<sub>OUT\_LK\_LS</sub> current **VB** = 13.5 **V** OUT1-4 Voltage S/R on/off  $V_{S/R\_s\_LS}$ 2 4 6 V/µs Load: 8  $\Omega$ , 10 nF – From "slow" 80% to 30% of OUTx VB = 13.5 V Voltage S/R on/off 5 10 15 V/µs  $V_{S/R_f_LS}$ Load: 8 Ω, 10 nF - From "fast" 80% to 30% of VOUT

Table 18. Low-side drivers OUT1-4 electrical characteristics

Low side driver L9301

Table 18. Low-side drivers OUT1-4 electrical characteristics (continued)

| Pin    | Symbol                   | Parameter                              | Test condition                                                              | Min. | Тур. | Max. | Unit |

|--------|--------------------------|----------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

|        | T <sub>turn-on_LS</sub>  | Turn-on delay time                     | From command to 80% OUTx, VB = 13.5 V Load: 8 $\Omega$ , 10 nF              | -    | -    | 3    | μs   |

|        | T <sub>turn-off_LS</sub> | Turn-off delay time                    | From command to 30%<br>OUTx, VB = 13.5 V<br>Load: 8 Ω, 10nF                 | -    | -    | 3    | μs   |

| OUT1-4 | V <sub>CL_LS</sub>       | Output clamping voltage                | I_load = 0.6 A T = 130 °C                                                   | 34   | 37.5 | 41   |      |

| 0011-4 |                          |                                        | I_load = 0.6A T= -40 °C and 25 °C                                           | 35   | 37.5 | 41   | V    |

|        | E <sub>clampSP_LS</sub>  | Clamp repetitive pulse energy ATE test | LS configuration<br>I_load = 0.7 A, T <sub>j</sub> = 150 °C,<br>100 kpulses | -    | -    | 5    | mJ   |

|        |                          | Clamp single pulse energy ATE test     | LS configuration<br>I_load = 0.7 A, T <sub>j</sub> = 150 °C                 | -    | -    | 10   |      |

### 9.2 Electrical characteristics OUT5-8

5 V  $\leq$  VB < 18 V; -40 °C  $\leq$   $T_{j}$   $\leq$  175 °C unless otherwise specified.

Table 19. Low-side drivers OUT5-8 electrical characteristics

| Pin    | Symbol                   | Parameter                    | Test condition                                                       | Min. | Тур. | Max. | Unit |

|--------|--------------------------|------------------------------|----------------------------------------------------------------------|------|------|------|------|

|        | R <sub>DS-on_LS</sub>    | Drain-source resistance      | I_load = 2 A                                                         | -    | -    | 0,3  | Ω    |

|        | I <sub>OUT_LK_LS</sub>   | Output leakage current       | OUTx = 13.5 V                                                        | -    | -    | 10   | μA   |

|        | V <sub>S/R_s_LS</sub>    | Voltage S/R on/off<br>"slow" | VB = 13.5 V<br>Load: 8 Ω, 10 nF – From 80% to 30% of OUTx            | 2    | 4    | 6    | V/µs |

| OUT5-8 | V <sub>S/R_f_LS</sub>    | Voltage S/R on/off<br>"fast" | VB = 13.5 V<br>Load: 8 $\Omega$ , 10 nF – From 80%<br>to 30% of VOUT | 5    | 10   | 15   | V/µs |

|        | T <sub>turn-on_LS</sub>  | Turn-on delay time           | From command to 80% OUTx Load: 8 Ω, 10 nF                            | -    | -    | 3    | μs   |

|        | T <sub>turn-off_LS</sub> | Turn-off delay time          | From command to 30% OUTx Load: 8 Ω, 10 nF                            | -    | -    | 3    | μs   |

|        |                          | Output clamping              | I_load = 1.25 A T = 130 °C                                           | 34   | 37.5 | 41   |      |

|        | $V_{CL\_LS}$             | voltage                      | I_load = 1.25 A T= -40 °C<br>and 25 °C                               | 35   | 37.5 | 41   | V    |

L9301 Low side driver

| Pin    | Symbol                  | Parameter                              | Test condition                                                              | Min. | Тур. | Max. | Unit |

|--------|-------------------------|----------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| OUT5-8 | E <sub>clampSP_LS</sub> | Clamp repetitive pulse energy ATE test | LS configuration<br>I_load = 2.2 A, T <sub>j</sub> = 150 °C,<br>100 kpulses | -    | -    | 15   | mJ   |

|        | E <sub>clampSP_LS</sub> | Clamp single pulse energy ATE test     | LS configuration<br>I_load = 2.2 A, T <sub>j</sub> = 150 °C                 | -    |      | 18.1 | mJ   |

Table 19. Low-side drivers OUT5-8 electrical characteristics (continued)

#### 9.3 Driver diagnostic

#### 9.3.1 Thermal protection

Each solenoid channel has a dedicated temperature sensor that continuously monitors the temperature of the power MOS.

In case the temperature shut down is reached the related channel is turned off and the dedicated diagnostic bits are set.  $t\_sd\_x$  is the bit that latches the thermal shut down and it is cleared after SPI read,  $t\_sd\_x$  is the other thermal shut down bit and once it is set by thermal shut down condition it is cleared only when the  $T_j$  decreases below the thermal shut down threshold (hysteresis). If the microcontroller, when the device is still in temperature shut down condition ( $t\_sd\_x = 1$ ), clears the  $t\_sd\_x$  and tries to turn on the output, the actuation will not be performed and the  $t\_sd\_x$  will be set again. To avoid these multiple interrupts the microcontroller can poll the  $t\_sd\_x$  bit and enable the next actuation only when the bit is zero.

#### 9.3.2 Overcurrent protection

An overcurrent protection is present for each driver OUT1...8. The overcurrent threshold is selectable through oc\_thres\_x (where x indicates the channel). In case of overcurrent the output driver is turned off, the related SPI command bit is set to 0 and a dedicated diagnostic bit is set oc x, where x indicates the channel where the fault occurred.

If bit oc\_restart = 0, to restart the channel the microcontroller has to clear the fault bit (reading the fault register), and to write to 1 the SPI command bit or to provide a rising edge on the parallel input command.

If bit oc\_restart = 1, the restart function is activated. The slew rate of the channel in fault condition is automatically set to the higher value to limit dissipation issue then to restart the channel the microcontroller has to write to 1 the SPI command bit or to provide a rising edge on the parallel input command. The diagnostic bit oc\_x can be cleared only by writing it to 0 in the corresponding driver status register by SPI however the channel can be restarted as described above.

#### 9.3.3 Output status

During the ON phase, the output voltage is compared with the VTopen threshold voltage in order to verify if the output status is aligned with the ON command. If the OUTx voltage is above the VTopen threshold a dedicated bit is set to indicate the anomaly.

Low side driver

#### 9.3.4 OFF state diagnostic

The device provides the off-state diagnostic for each channel.

The short to ground and open load faults can be detected. The fault is reported in a SPI register.

Figure 12. LS configuration diagnostic

Table 20. LS diagnostic

| DIAGOL | DIAGLV | FAULT DETECTION |

|--------|--------|-----------------|

| 0      | 0      | no fault        |

| 0      | 1      | not possible    |

| 1      | 0      | open load       |

| 1      | 1      | short to ground |

The diagnostic blanking time is configurable through the dedicated diagoff\_blank\_sel bit.

#### 9.3.5 DLOSS

In case the device is configured as low side and external diodes are used for freewheeling, there is the possibility through a dedicated SPI bit to enable the 'diode loss' diagnosis that is used to detect if the external diode is no more connected checking if during the OFF phase the internal clamp is activated. Another SPI bit allows to configure the actions to be taken in case of DLOSS fault.

5//

L9301 Low side driver

### 9.3.6 OC comparator self-test

L9301 provides driver OC comparator self-test function. During OFF phase, the OC comparator still works and the expected result is '1' due to high VDS. If L9301 detects OC '0' during OFF phase, the SPI bit oc\_comparator\_f is set to '1'.

For OUT1-8, if a STG fault is present at OFF phase, the OC comparator inputs are still forced to have OC '1'.

#### 9.3.7 Electrical characteristics related to diagnosis

Table 21. Electrical characteristics related to diagnosis

| Pin    | Symbol                                 | Parameter                                              | Test condition      | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------|--------------------------------------------------------|---------------------|------|------|------|------|

|        | T <sub>Over_temperature_blanking</sub> | Over temperature blanking time                         | Tested by scan      | 1    | -    | 1.5  | μs   |

|        | T <sub>Over_temperature_filter</sub>   | Over temperature filter time                           | Tested by scan      | 2    | -    | 5    | μs   |

|        | R <sub>open_load_LS</sub>              | Min. resistor value open load detection                | Not tested          | 500  | -    | -    | kΩ   |

|        | I <sub>MAX_LS</sub>                    | Output current                                         | Not tested          | -    | 2.2  | -    | Α    |

|        | I <sub>OVC1_OUT1-4</sub>               | Over current threshold1 OUT1-4                         | -                   | 1    | 2    | 3    | Α    |

|        | I <sub>OVC2_OUT1-4</sub>               | Over current threshold2 OUT1-4                         | -                   | 3    | 4    | 5    | А    |

|        | I <sub>OVC1_OUT5-8</sub>               | Over current threshold1 OUT5-8                         | -                   | 2    | 4    | 6    | Α    |

|        | I <sub>OVC2_OUT5-8</sub>               | Over current threshold2 OUT5-8                         | -                   | 6    | 8    | 10   | А    |

| OUT1-8 | T <sub>FLT_OVC_LS</sub>                | Over current filtering time                            | Tested by scan      | 3    | -    | 5    | μs   |

|        | T <sub>FLT_diagoff_</sub> LS           | Filtering open load<br>and short to GND<br>diag. off   | Tested by scan      | 55   | -    | 80   | μs   |

|        | T <sub>d_blank0_LS</sub>               | Diagnosis blanking time after switch-off               | Tested by scan      | 600  | -    | 900  | μs   |

|        | T <sub>d_blank1_LS</sub>               | Diagnosis blanking time after switch-off               | Tested by scan      | 300  | -    | 450  | μs   |

|        | V <sub>TOPEN_LS</sub>                  | Open load threshold voltage                            | -                   | 2.7  | -    | 3.1  | V    |

|        | V <sub>OUTOPEN_LS</sub>                | Open load output voltage                               | Open load condition | 2,3  | 2.5  | 2,7  | V    |

|        | $V_{TGND\_LS}$                         | Output short-circuit to GND voltage threshold          | -                   | 1.9  | -    | 2.3  | V    |

|        | I <sub>OUT_PD_LS</sub>                 | Output diagnostic pull-<br>down current @ OFF<br>STATE | OUTx = 5 V          | 40   | 70   | 100  | μА   |

Low side driver L9301

Table 21. Electrical characteristics related to diagnosis (continued)

| Pin    | Symbol                 | Parameter                                              | Test condition                                          | Min. | Тур. | Max. | Unit |

|--------|------------------------|--------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

|        | I <sub>OUT_PU_LS</sub> | Output diagnostic pull-<br>up current @ OFF<br>STATE   | OUTx=1.5 V                                              | 50   | 75   | 100  | μА   |

| OUT1-8 | -                      | Minimum OFF time for correct diagnostic (Blank time 0) | Application note<br>(ESD cap < 12 nF,<br>Bit_blank = 0) | 980  | -    | -    | μs   |

|        | -                      | Minimum OFF time for correct diagnostic (Blank time 1) | Application note<br>(ESD cap < 6 nF,<br>Bit_blank = 1)  | 530  | -    | -    | μs   |

### 10 Combined diagnosis (configuration 1, 2 & 3)

In configuration 1, there are four couples of drivers in parallel to get four channels with lower RdsON: OUT1 with OUT2, OUT3 with OUT4, HS1 with HS2, and HS3 with HS4. For each couple, only one driver off diagnosis is enabled (OUT1, OUT3, HS1, HS3) while the off diagnosis results are stored in both drivers registers. The other diagnosis of the two drivers in parallel, as over-current, over-temperature and DLOSS, are both enabled.

In configuration 2 the off diagnosis is enabled for OUT1-4 only. Considering that the diagnosis blanking time can be longer than the off time of PWM, the diagnosis results can be affected. The short to GND fault can be detected by the HS OC fault when it is switched on. The Open Load Fault can be detected when PWM is disabled (PWM disable SPI bit = 1) only because in such a condition both HS and LS are OFF. In this condition the OUTx is pulled down by LS off diagnosis pull down current (typical 70  $\mu$ A) and it's necessary to wait the time needed to discharge OUTx to get Open Load (OL) detection. The time to be considered starts from the PWM disable bit writing.

Max. **Parameter Test condition** Min. Unit Typ. Minimum OFF time for Application note NOT TESTED 4140 correct diagnostic (Blank μs (ESD cap < 12 nF, Bit blank = 0) time 0) Minimum OFF time for Application note NOT TESTED correct diagnostic (Blank 2190 μs (ESD cap < 6 nF, Bit blank=1) time 1)

Table 22. Configuration 2

In configuration 3 the off diagnosis is enabled for HS1-4 only. Considering that the diagnosis blanking time can be longer than the off time of PWM, the diagnosis results can be affected. The short to VB fault can be detected by the OC fault when it is switched on. The Open Load Fault can be detected when PWM is disabled (PWM disable SPI bit = 1) only because in such a condition both HS and LS are OFF. In this condition the OUTx is pulled up by HS off diagnosis pull up current (typical 75  $\mu$ A) and it's necessary to wait the time needed to discharge OUTx to get Open Load (OL) detection. The time to be considered starts from the PWM disable bit writing.

Table 23. Configuration 3

| Parameter                                              | Test condition                                               | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

| Minimum OFF time for correct diagnostic (Blank time 0) | Application note NOT TESTED (ESD cap < 12 nF, Bit_blank = 0) | 980  | -    | -    | μs   |

| Minimum OFF time for correct diagnostic (Blank time 1) | Application note NOT TESTED (ESD cap < 6 nF, Bit_blank=1)    | 530  | -    | -    | μs   |

In PWM mode, configuration 2 and 3, unless the PWM enable SPI bit for OUT1-4 and DRN/SRC1-4 are set, the eight drivers are all switched off.

BIST L9301

### 11 BIST

After VDD and VB power on with RES = Hi, SCK = Lo a digital logic BIST (build-in self-test) it's started and it takes max 11ms to be completed. The BIST status register (0x1E) contains three bits to reflect the status of BIST.

The purpose of logic BIST is to test manufacturing or aging defect. If the BIST ends with an error, the device is no longer reliable.

While the BIST is running, the device is not operable.

When EN pin voltage is higher than 25 V, the device enters test mode and BIST run will abort immediately.

The oscillator FLL is enabled after BIST run (clkch\_en bit).

L9301 Clock monitor

### 12 Clock monitor

For safety reasons the device has two clock signals: main clock and diagnosis clock.

The diagnosis clock is a redundant oscillator which has been introduced with the aim to perform a frequency check with the main clock. A dedicated digital block is present to accomplish this task.

If a clock signal is running out of range, a status bit is set (clkbad). In case the main clock stops working, a digital internal reset is asserted, until POR or RES clears it.

If the main clock is running 25% faster or slower than diagnosis clock, the bit clkbad is set.

If the main clock is running 85% slower than diagnosis clock, a digital internal reset is asserted, the device is put to reset state, all drivers are off and no response to any input signal is given, until power off or RES pin assert (RES pin set to '0') to clear it.

Table 24. Clock monitor

| Parameter            | Test condition | Min. | Тур. | Max. | Unit |

|----------------------|----------------|------|------|------|------|

| Main clock frequency | -              | -    | 5    | -    | MHz  |

SPI L9301

## 13 SPI

The SPI interface is used to configure the device, control the output and read the diagnostic and output status registers.

Every time a bit in one of the SPI registers is set by the L9301 (for example when an error is detected) it will not be reset until the corresponding registers have been read out via SPI. The bit will not be reset if an SPI error occurs during access to register by the  $\mu C$  or while L9301 sends the content of the register as an answer.

## 13.1 CS, SCK, MOSI

Table 25. CS, SCK, MOSI

| Pin              | Symbol | Parameter                | Test condition                                         | Min. | Тур. | Max.    | Unit |

|------------------|--------|--------------------------|--------------------------------------------------------|------|------|---------|------|

|                  | V_IH   | Logic input high voltage | -                                                      | 1.75 | -    | VDD+0.3 | V    |

|                  | V_IL   | Logic input low voltage  | -                                                      | -0.3 | -    | 0.75    | V    |

| CS, SCK,<br>MOSI | V_lhys | Logic input hysteresis   | -                                                      | 100  | -    | 1000    | mV   |

|                  | lin    | Input current            | -                                                      | -    | -    | 5       | μA   |

|                  | Ri_pu  | Pull up resistor         | Tested at 1.5 V,<br>R = (3.3-1.5)/I <sub>measure</sub> | 50   | -    | 250     | kΩ   |

## 13.2 MISO

Back supply current into supply pin of MISO is not allowed.

Back to Back structure: in case of an over-voltage condition at the MISO output, the HS path (Back to Back) has to be switched off after tOFF\_PROT by analog circuitry to avoid back supply current into supply pin of SDO.

#### **Protection of SDO Output**

The internal LS driver must withstand a direct short circuit to battery (current limitation or shutdown possible, no destruction allowed).

The internal HS driver must withstand a direct short circuit to GND (current limitation or shutdown possible, no destruction allowed).

Table 26. MISO

| Pin   | Symbol    | Parameter                                                 | Test condition             | Min.        | Тур. | Max.      | Unit     |

|-------|-----------|-----------------------------------------------------------|----------------------------|-------------|------|-----------|----------|

|       | V_OH      | Logic output high voltage                                 | I <sub>sink</sub> = 2 mA   | VDD_I/O-0.4 | 1    | -         | ٧        |

| MISO  | V_OL      | Logic output low voltage                                  | I <sub>source</sub> = 2 mA |             | ı    | 0.4       | <b>V</b> |

| WIIGO | VOV_MISO  | Over voltage detection threshold at MISO output           | -                          | VDDIO+0.05  | 1    | VDDIO+0.2 | <b>V</b> |

|       | tOFF_PROT | Turn OFF delay for over voltage reverse supply protection | -                          | 0           | -    | 1.5       | μs       |

## 13.3 SPI frame

#### MOSI

| 31  | 30        | 29 | 28 | 27  | 26 | 25 | 24 | 23  | 22 | 21 | 20 | 19    | 18  | 17 | 16 |

|-----|-----------|----|----|-----|----|----|----|-----|----|----|----|-------|-----|----|----|

| W/R |           |    |    | ADD |    |    |    | RES |    |    | DA | TA[19 | 13] |    |    |

| 15  | 14        | 13 | 12 | 11  | 10 | 9  | 8  | 7   | 6  | 5  | 4  | 3     | 2   | 1  | 0  |

|     | DATA[120] |    |    |     |    |    |    |     |    |    |    |       |     |    | )] |

W/R 1 = Write

0 = Read

ADD Address RES Reserved

DATA Data

CRC CRC: Polynomial is  $x^3+x^2+x+1$

#### **MISO**

| 31 | 30        | 29  | 28 | 27 | 26    | 25    | 24 | 23 | 22 | 21 | 20    | 19  | 18 | 17    | 16 |

|----|-----------|-----|----|----|-------|-------|----|----|----|----|-------|-----|----|-------|----|

| SI | PIErr[2.  | .0] |    |    | CHExc | p[50] |    |    |    | DA | TA[19 | 13] |    |       |    |

| 15 |           |     |    |    |       |       |    |    |    |    |       |     | 1  | 0     |    |

|    | DATA[120] |     |    |    |       |       |    |    |    |    |       |     |    | RC[20 | 0] |

SPIErr[2] SPI Short Frame: a less-than-32bit SPI frame was received

SPIErr[1] SPI Long Frame: a more-than-32bit SPI frame was received

SPIErr[0] SPI CRC Error: SPI CRC checksum error

CHExcp[5] gf: bit 6 of General device diagnostic register

CHExcp[4] got: bit 4 of General device diagnostic register

CHExcp[3] vdduv: bit 3 of General device diagnostic register

CHExcp[2] vddov: bit 2 of General device diagnostic register

CHExcp[1] vbuv: bit 1 of General device diagnostic register

CHExcp[0] vbov: bit 0 of General device diagnostic register

DATA Data

CRC CRC: Polynomial is x3+x2+x+1

# 13.4 SPI registers

# CR0(0x00)

#### Device general configuration register

| 19         | 18         | 17         | 16         | 15         | 14         | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1                 | 0       |

|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------------------|---------|

|            |            |            | RESE       | RVED       |            |            |            |            | conf4      | lshs       |            | dloss_conf | cpl_conf   | vdduv_conf | vddov_conf | vbuv_conf  | vbov_conf  | Cultout conf[1-0] |         |

| 0<br>(R/W) | (R/               | )<br>W) |

#### [19:12] RESERVED: Reserved

- [11] conf4\_lshs[3]

- 0 = HS is configured as high side driver during configuration4

- 1 = HS is configured as low side driver during configuration4

- [10] conf4\_lshs[2]

- 0 = HS is configured as high side driver during configuration4

- 1 = HS is configured as low side driver during configuration4

- [9] conf4\_lshs[1]

- 0 = HS is configured as high side driver during configuration4

- 1 = HS is configured as low side driver during configuration4

- [8] conf4\_lshs[0]

- 0 = HS is configured as high side driver during configuration4

- 1 = HS is configured as low side driver during configuration4

- [7] dloss\_conf

- 0 = no auto shut driver when freewheeling diode loss

- 1 = auto shut driver when freewheeling diode loss

- [6] cpl conf

- 0 = no auto shut driver when charge pump low

- 1 = auto shut driver when charge pump low

- [5] vdduv conf

- 0 = no auto shut driver when vdduv

- 1 = auto shut driver when vdduv

- [4] vddov\_conf

- 0 = no auto shut driver when vddov

- 1 = auto shut driver when vddov

- [3] vbuv\_conf

- 0 = no auto shut driver when vbuv

- 1 = auto shut driver when vbuv

- [2] vbov\_conf

- 0 = no auto shut driver when vbov

- 1 = auto shut driver when vbov

- [1:0] output\_conf (1)

| output_conf[1] | output_conf[0] | Configuration |

|----------------|----------------|---------------|

| 0              | 0              | 1             |

| 0              | 1              | 2             |

| 1              | 0              | 3             |

| 1              | 1              | 4             |

1. Output\_conf bits can only be modified when EN pin is logic 0

## CR1-CR12 (0x01-0x0C)

## **Device configuration register**

| 19    | 18    | 17    | 16    | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | 7      | 6           | 5          | 4         | 3                 | 2          | 1        | 0         |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|-------------|------------|-----------|-------------------|------------|----------|-----------|

|       |       |       |       |       | RESE  | RVED  |       |       |       |       |       | pwm_en | dis_diagoff | dis_source | dloss_act | diagoff_blank_sel | oc_restart | oc_thres | slew_rate |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0      | 0           | 0          | 0         | 0                 | 0          | 0        | 0         |

| (R/W)  | (R/W)       | (R/W)      | (R/W)     | (R/W)             | (R/W)      | (R/W)    | (R/W)     |

- [19:8] RESERVED: Reserved

- [7] pwm\_en

- 0 = driver is disabled

- 1 = driver is enabled

- available only in LS4-1 and HS4-1, used for diagoff test in configuration 2/3

- [6] dis\_diagoff

- 0 = enable off diagnosis

- 1 = disable off diagnosis

- [5] dis\_source

- 0 = enable off diagnosis pull up current

- 1 = disable off diagnosis pull up current

- [4] dloss\_act

- 0 = disable the dloss signal diagnosis

- 1 = enable the dloss signal diagnosis

- [3] diagoff\_blank\_sel

- 0 = long blanking time

- 1 = short blanking time

- [2] oc\_restart

- 0 = restart the channel only after clearing the fault bit

- 1 = restart the channel without clearing the fault bit

- [1] oc\_thres

- 0 = normal over current threshold

- 1 = enable double over current threshold