# The fido1100<sup>®</sup> User Guide for the 32-Bit Real-Time Communications Controller

Copyright © 2009 by Innovasic Semiconductor, Inc. Published by Innovasic Semiconductor, Inc. 3737 Princeton Drive NE, Suite 130, Albuquerque, NM 87107

fido<sup>®</sup>, fido1100<sup>®</sup>, and SPIDER™ are trademarks of Innovasic Semiconductor, Inc. I2C™ Bus is a trademark of Philips Electronics N.V. Motorola<sup>®</sup> is a registered trademark of Motorola, Inc.

# **TABLE OF CONTENTS**

| List ( | of Fig               | gures                                   | 8  |  |

|--------|----------------------|-----------------------------------------|----|--|

| List o | of Tal               | ıbles                                   | 9  |  |

| Conv   | entio                | ons                                     | 15 |  |

| Nom    | encla                | ature                                   | 16 |  |

| Safet  | y Info               | formation                               | 17 |  |

| Prefa  | ice                  |                                         | 18 |  |

| 1.     | Intro                | oduction to fido1100 Architecture       | 19 |  |

|        | 1.1                  | Features                                | 19 |  |

|        | 1.2                  | Architectural Overview                  | 20 |  |

|        |                      | 1.2.1 Core CPU                          | 20 |  |

|        |                      | 1.2.2 Memory Management                 | 21 |  |

|        |                      | 1.2.3 External Bus Interface            | 21 |  |

|        |                      | 1.2.4 PMU/UIC/CPU DMA                   | 22 |  |

|        |                      | 1.2.5 Internal Peripherals              | 22 |  |

|        |                      | 1.2.6 JTAG/Debug                        | 22 |  |

|        | 1.3                  | Programming Model                       |    |  |

|        |                      | 1.3.1 CPU32 Instruction Set Compatible  |    |  |

|        |                      | 1.3.2 Memory-Mapped Address Space       |    |  |

| 2.     | Prog                 | grammer Reference Overview              |    |  |

|        | 2.1                  | User Guide Structure                    | 25 |  |

|        | 2.2                  | Chapter Overview                        | 26 |  |

| 3.     | Context Architecture |                                         |    |  |

|        | 3.1                  | Introduction                            |    |  |

|        | 3.2                  | Context Types and Operational Modes     |    |  |

|        |                      | 3.2.1 Standard Context                  |    |  |

|        |                      | 3.2.2 Fast-Vectored Context             |    |  |

|        |                      | 3.2.3 Fast Single-Thread Context        |    |  |

|        | 3.3                  | Master Context                          |    |  |

|        | 3.4                  | Summary                                 |    |  |

| 4.     | Core                 | e CPU                                   |    |  |

|        | 4.1                  | Overview                                |    |  |

|        | 4.2                  | Address and Data Space                  |    |  |

|        | 4.3                  | •                                       |    |  |

|        |                      | 4.3.1 Data Register Operands            |    |  |

|        |                      | 4.3.2 Address Register Operands         |    |  |

|        |                      | 4.3.3 Operands in Memory                |    |  |

|        | 4.4                  | * · · · · · · · · · · · · · · · · · · · |    |  |

|        | 4.5                  | 1 1                                     |    |  |

|        |                      | 4.5.1 Data Movement Instructions        |    |  |

|        |                      | 4.5.2 Integer Arithmetic Operations     |    |  |

|        |                      | - r                                     | ,  |  |

|     | 4.5.3   | Logic Instructions                                 | 38  |

|-----|---------|----------------------------------------------------|-----|

|     | 4.5.4   | Shift and Rotate Instructions                      | 38  |

|     | 4.5.5   | Bit Manipulation Instructions                      | 38  |

|     | 4.5.6   | Binary-Coded Decimal Instructions                  | 38  |

|     | 4.5.7   | Program Control Instructions                       | 39  |

|     | 4.5.8   | System Control Instructions                        | .39 |

|     | 4.5.9   | Power Control Instructions                         | .39 |

|     | 4.5.10  | Modifications to CPU32 Instruction Compatibility   | 39  |

|     |         | New Instructions                                   |     |

| 4.6 | Interru | pts, Faults and Exceptions                         | .40 |

|     | 4.6.1   | Overview                                           | .40 |

|     | 4.6.2   | External Interrupts                                | .41 |

|     | 4.6.3   | Interrupt Priorities and Control                   | .43 |

|     | 4.6.4   | Interrupt, Fault and Exception Handling            | .45 |

|     | 4.6.5   | Summary                                            |     |

| 4.7 | Reset I | Processing                                         |     |

| 4.8 | Contex  | t Management                                       | .60 |

|     | 4.8.1   | Overview                                           | .60 |

|     | 4.8.2   | Master Context                                     | .61 |

|     | 4.8.3   | Context Priorities                                 | .61 |

|     | 4.8.4   | Context Modes                                      | 62  |

|     | 4.8.5   | Context States                                     | .62 |

|     | 4.8.6   | Contexts and Interrupts                            | .64 |

|     | 4.8.7   | Context Timers                                     | .64 |

|     | 4.8.8   | Context Initialization                             | .65 |

|     | 4.8.9   | Context Claim Registers                            | .66 |

|     | 4.8.10  | Software Interrupt Control and Actuation Registers | .67 |

|     | 4.8.11  | Context Management Registers                       | .68 |

|     | 4.8.12  | Context Control Register                           | .68 |

|     | 4.8.13  | Context Timer Enable Register                      | .69 |

|     | 4.8.14  | Context Timer Register                             | .71 |

|     | 4.8.15  | Context Maximum Time Register                      | .72 |

|     | 4.8.16  | Context Timer Clear Register                       | 73  |

|     |         | Context Idle Timer Register                        |     |

|     | 4.8.18  | Context Claim Register Set                         | .74 |

|     | 4.8.19  | Software Interrupt Register Set                    | .77 |

|     |         | Software Interrupt Control Register                |     |

|     | 4.8.21  |                                                    |     |

| Men | nory Ma | nagement and Protection                            | .79 |

| 5.1 |         | ew                                                 |     |

| 5.2 | The fid | o1100 Internal Memory and Registers                | .79 |

| 5 3 |         | 1 SR AM                                            | 79  |

5.

|    | 5.4   | Internal Relocatable Rapid Execution Memory                     | 80  |

|----|-------|-----------------------------------------------------------------|-----|

|    | 5.5   | Re-Mapping Example                                              | 81  |

|    | 5.6   | Endian Mode Control                                             | 82  |

|    | 5.7   | Definitions                                                     | 82  |

|    | 5.8   | MOVEC Access-Based Registers                                    | 83  |

|    | 5.9   | Source Function Code Register (0x000)                           | 84  |

|    | 5.10  | Destination Function Code Register (0x001)                      |     |

|    |       | User Stack Pointer Register (0x800)                             |     |

|    | 5.12  | Vector Base Register (0x801)                                    | 86  |

|    | 5.13  | Configuration Access Control Register (0xFFE)                   | 86  |

|    |       | Memory Base Offset Register (0xFFF)                             |     |

|    | 5.15  | Memory and Register Group Address Map                           | 87  |

|    |       | Memory Protection Unit                                          |     |

|    | 5.17  | MPU Block Control Base Register                                 | 91  |

|    |       | MPU Block Control Attributes Register                           |     |

|    |       | CTX MPU Allocation Registers                                    |     |

|    | 5.20  | MPU Example                                                     | 93  |

|    |       | Programmable Chip Select Registers                              |     |

|    | 5.22  | Complete Register Address Map                                   | 95  |

| 6. | Exte  | rnal Bus Interface                                              | 129 |

|    | 6.1   | Address and Data Bus                                            | 130 |

|    | 6.2   | External Bus Chip Select Control and Timing Registers           | 131 |

|    |       | 6.2.1 External Bus Chip Select Control Register_N (where N=07)  |     |

|    |       | 6.2.2 External Bus Chip Select Timing Register_N (where N=07)   |     |

|    | 6.3   | External Bus Default Timing Register                            |     |

|    | 6.4   | External Bus Priority Register                                  |     |

|    | 6.5   | SDRAM Controller Registers                                      | 137 |

|    |       | 6.5.1 SDRAM Timing Parameter 0 Register                         | 138 |

|    |       | 6.5.2 SDRAM Timing Parameter 1 Register                         | 140 |

|    |       | 6.5.3 SDRAM Configuration 0 Register                            | 140 |

|    |       | 6.5.4 SDRAM Configuration 1 Register                            | 142 |

|    |       | 6.5.5 SDRAM External Bank Configuration Register_N (where N=07) |     |

|    | 6.6   | Startup and Operation of SDRAM Controller                       |     |

|    |       | 6.6.1 Initial Setups                                            | 144 |

|    |       | 6.6.2 Setups for SDRAM Controller Examples                      |     |

|    | 6.7   | SDRAM Module Types Address Mapping (16-Bit Bus Width)           | 148 |

|    | 6.8   | SDRAM Module Types Address Mapping (8-Bit Bus Width)            |     |

|    | 6.9   | SDRAM External I/O Signal List                                  |     |

|    | 6.10  | External Bus Arbitration                                        |     |

| 7. | Perip | oheral Management Unit                                          | 151 |

|    | 7.1   | PMU                                                             | 151 |

|    |       | 7.1.1 Overview                                                  | 151 |

|    |       | 7.1.2      | Interrupts                                      | 156 |

|----|-------|------------|-------------------------------------------------|-----|

|    |       | 7.1.3      | PMU Registers                                   | 159 |

|    |       | 7.1.4      | PMU Usage                                       | 168 |

|    |       | 7.1.5      | Buffer Access Modes                             | 169 |

|    |       | 7.1.6      | Packet Size Insertion                           | 172 |

|    | 7.2   | Unive      | ersal I/O Controller (UIC)                      | 172 |

|    |       | 7.2.1      | Overview                                        | 172 |

|    |       | 7.2.2      | UIC GPIO Registers                              | 173 |

|    |       | 7.2.3      | UIC Configuration Registers                     | 180 |

|    |       | 7.2.4      | UIC Interrupt Registers                         | 184 |

|    |       | 7.2.5      | UIC Programming                                 | 185 |

|    |       | 7.2.6      | UIC Sleep Mode                                  | 186 |

|    | 7.3   | <b>DMA</b> | (Direct Memory Access Controllers)              | 187 |

|    |       | 7.3.1      | Overview                                        | 187 |

|    |       | 7.3.2      | DMA Registers                                   | 188 |

|    |       | 7.3.3      | DMA Setup                                       | 193 |

|    | 7.4   | MAC        | Filter                                          |     |

|    |       | 7.4.1      | MAC Filter Overview                             | 194 |

|    |       | 7.4.2      | MAC Filter Registers                            | 196 |

|    |       | 7.4.3      | MAC Filter RAM organization for HASH Table Mode | 199 |

|    |       | 7.4.4      | MAC Filter Setup                                |     |

| 8. | Inter | nal Per    | ipherals                                        | 201 |

|    | 8.1   | System     | m Timer                                         | 201 |

|    |       | 8.1.1      | Overview                                        | 201 |

|    |       | 8.1.2      | System Timer Interrupt Calculation              | 203 |

|    |       | 8.1.3      | System Timer Registers                          |     |

|    |       | 8.1.4      | System Timer Setup                              |     |

|    | 8.2   | Watch      | ndog Timer                                      | 207 |

|    |       | 8.2.1      | Overview                                        |     |

|    |       | 8.2.2      | Watchdog Timer Registers                        | 208 |

|    |       | 8.2.3      | Watchdog Timer Setup                            |     |

|    | 8.3   | Timer      | Counter Units                                   |     |

|    |       | 8.3.1      | Overview                                        | 210 |

|    |       | 8.3.2      | TCU Timing Calculation                          |     |

|    |       | 8.3.3      | Timer Counter Unit Registers                    |     |

|    |       | 8.3.4      | TCU Setup                                       |     |

|    | 8.4   | Analo      | g-to-Digital Converter                          |     |

|    |       | 8.4.1      | Overview                                        |     |

|    |       | 8.4.2      | ADC Registers                                   |     |

|    |       | 8.4.3      | ADC Setup                                       |     |

| 9. | Deb   | ug Feat    | ures                                            |     |

|    |       | _          | view                                            |     |

|     |      | 9.1.1    | Context Awareness                                           | 229 |

|-----|------|----------|-------------------------------------------------------------|-----|

|     |      | 9.1.2    | Breakpoints, Watchpoints, and Tracing                       | 229 |

|     |      | 9.1.3    | Examples                                                    |     |

|     |      | 9.1.4    | Summary                                                     |     |

|     | 9.2  | JTAG     | *                                                           |     |

|     | 9.3  | Debug    | Feature Associated Registers                                | 231 |

|     |      | 9.3.1    | Software Breakpoint Instruction                             |     |

|     |      | 9.3.2    | S/W BKPT                                                    |     |

|     | 9.4  | Hardw    | vare Breakpoints and Watchpoints                            | 233 |

|     |      | 9.4.1    | Watchpoint Block Size and Break/Watch Mode Control Register |     |

|     |      | 9.4.2    | Breakpoint and Watchpoint Chaining                          |     |

|     |      | 9.4.3    | Breakpoint Address/Watchpoint Base Address Register         |     |

|     |      | 9.4.4    | Watchpoint Data Register                                    |     |

|     |      | 9.4.5    | Watchpoint Data Mask Register                               | 237 |

|     | 9.5  | Trace    | Capability                                                  | 238 |

|     |      | 9.5.1    | Instruction Tracing Mode                                    | 240 |

|     |      | 9.5.2    | Trace Buffer Mode                                           | 241 |

|     | 9.6  | Debug    | Feature Examples                                            | 242 |

| 10. | Pow  | er Cont  | rol                                                         | 247 |

|     | 10.1 | Overv    | iew                                                         | 247 |

|     | 10.2 | Power    | -Saving Modes                                               | 247 |

|     | 10.3 | Detail   | ed Register Definition                                      | 252 |

|     |      | 10.3.1   | Power-On Reset Register                                     | 252 |

|     |      | 10.3.2   | Clock Mask Register                                         | 253 |

| 11. | Acce | ess-Con  | trolled Registers                                           | 255 |

|     | 11.1 | Overv    | iew                                                         | 255 |

|     | 11.2 | Config   | guration Access Control Register                            | 255 |

| 12. |      |          | p Reference                                                 |     |

| 13. | Revi | sion Hi  | story                                                       | 312 |

| 14  | For  | Addition | nal Information                                             | 313 |

# **LIST OF FIGURES**

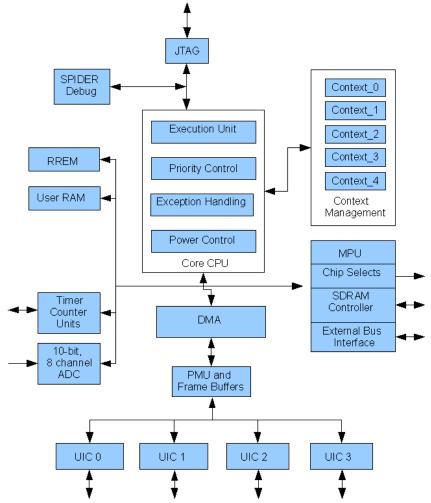

| Figure 1-1. | Diagram of the fido1100 Communications Controller | 21  |

|-------------|---------------------------------------------------|-----|

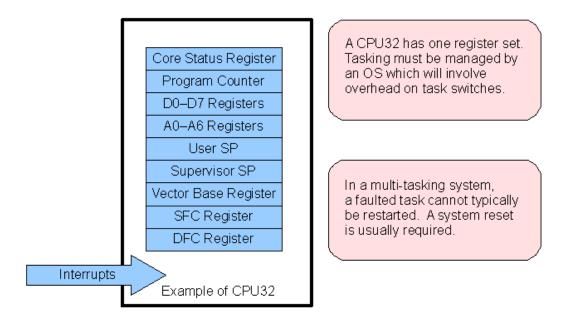

| Figure 3-1. | Standard Microprocessor, Single Context View      | 27  |

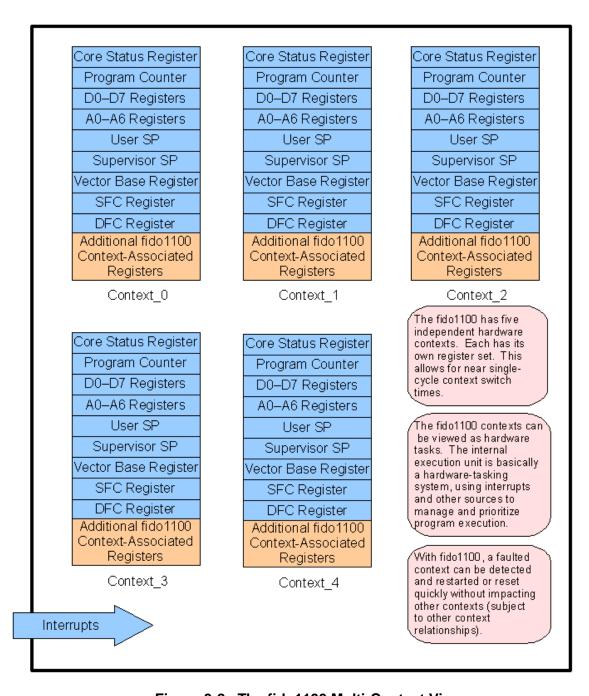

| Figure 3-2. | The fido1100 Multi-Context View                   | 29  |

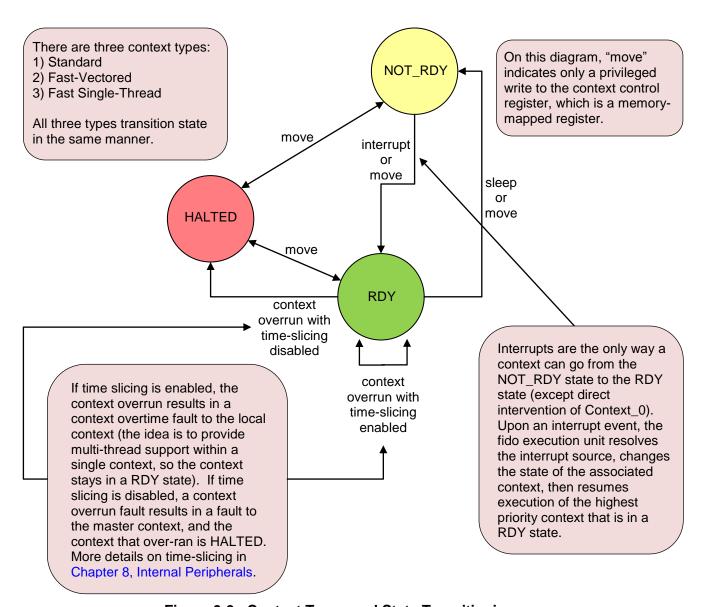

| Figure 3-3. | Context Types and State Transitioning             | 30  |

| Figure 3-4. | Context Interrupt Overhead                        | 31  |

| Figure 4-1. | Context and Interrupt Priority Processing         | 44  |

| Figure 4-2. | Sample System                                     | 63  |

| Figure 5-1. | The fido1100 Internal Memory and Registers        | 80  |

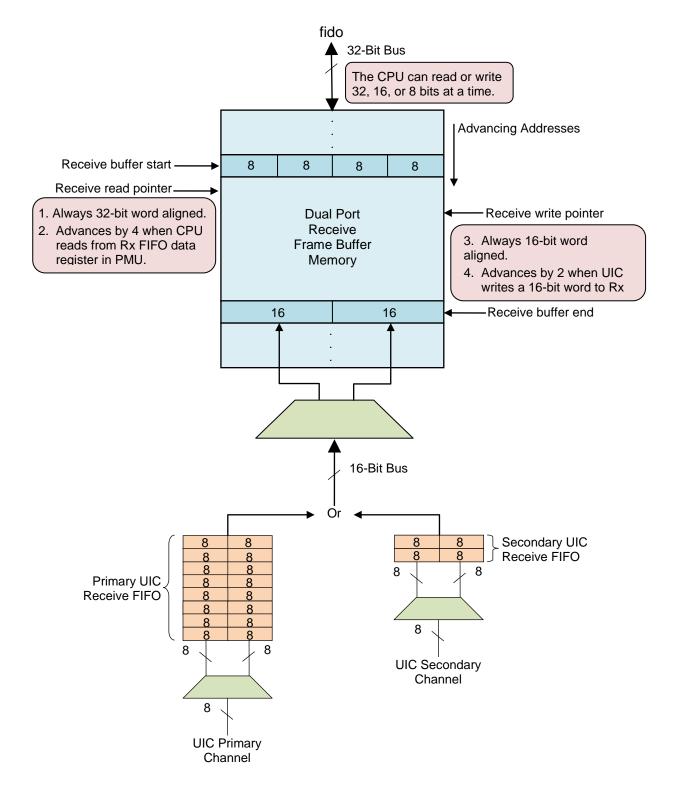

| Figure 7-1. | Diagram of the Dual-Port Receive RAM              | 152 |

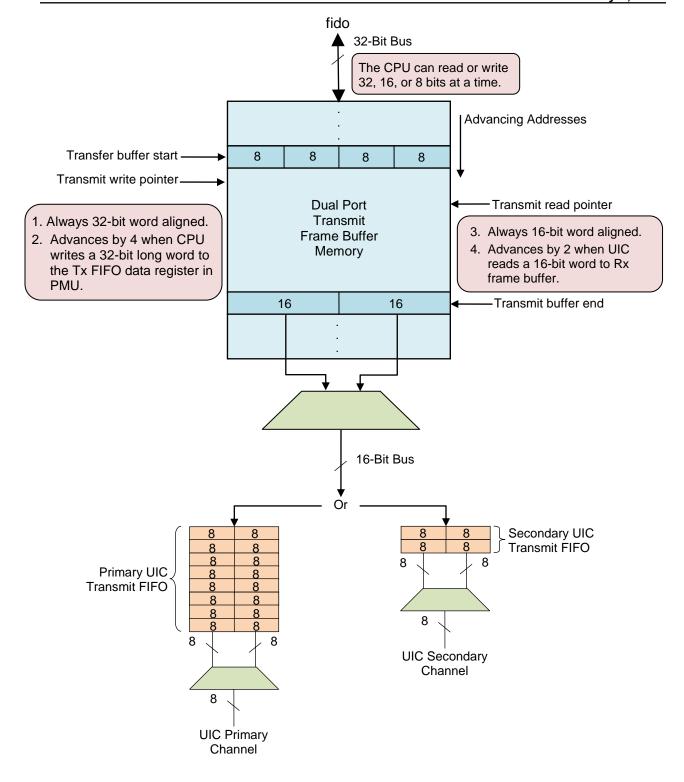

| Figure 7-2. | Diagram of the Dual-Port Transmit RAM             | 153 |

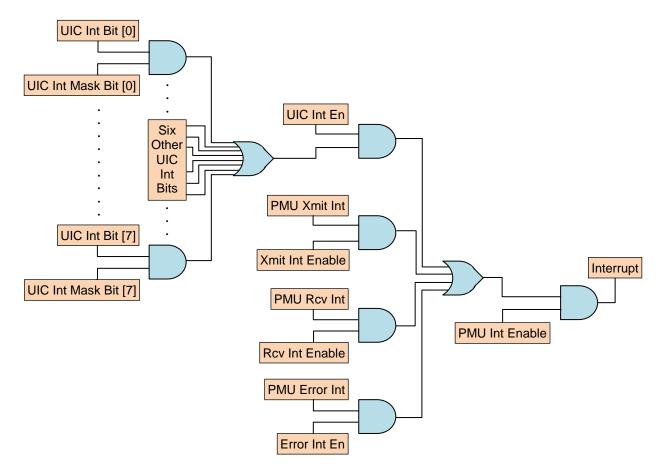

| Figure 7-3. | Diagram of PMU Interrupts                         | 157 |

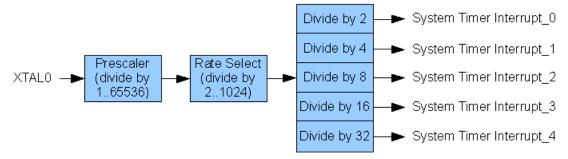

| Figure 8-1. | System Timer                                      | 201 |

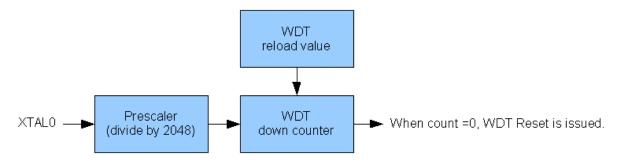

| Figure 8-2. | Watchdog Timer                                    | 207 |

# **LIST OF TABLES**

| Table 4-1. External Hardware Signals                                                       | .41 |

|--------------------------------------------------------------------------------------------|-----|

| Table 4-2. Interrupt 'N' Control Registers (where N=07)                                    |     |

| Table 4-3. Status Register                                                                 |     |

| Table 4-4. Short Format Stack Frame Offset Word Format/Vector                              | .46 |

| Table 4-5. Instruction Error Stack Frame Offset Word Format/Vector                         | .47 |

| Table 4-6. Trace Exception Instruction Error Generation                                    | .52 |

| Table 4-7. Faulted Context Register                                                        |     |

| Table 4-8. Exception Vector Table                                                          | .57 |

| Table 4-9. Sample Context Control Register                                                 | .62 |

| Table 4-10. Description of Context Timers Registers                                        | .64 |

| Table 4-11. Description of Context Claim Register                                          | .66 |

| Table 4-12. Example of Context Claim Register Implementation                               | .66 |

| Table 4-13. Description of Software Interrupt Control and Actuation Registers              | .67 |

| Table 4-14. Description of Context Management Registers                                    | .68 |

| Table 4-15. Context Control Register                                                       | .68 |

| Table 4-16. Context Timer Enable Register                                                  |     |

| Table 4-17. Context Timer Counter Register                                                 |     |

| Table 4-18. Context Maximum Time Register                                                  | .73 |

| Table 4-19. Context Timer Clear Register                                                   |     |

| Table 4-20. Context Idle Timer Register                                                    |     |

| Table 4-21. Context Claim Priority Inheritance Register                                    |     |

| Table 4-22. Pending Contexts Register                                                      |     |

| Table 4-23. Claim Register                                                                 |     |

| Table 4-24. Claim Register Example                                                         |     |

| Table 4-25. Software Interrupt Control Register                                            |     |

| Table 4-26. Software Interrupt Actuation Register                                          |     |

| Table 5-1. Relocatable RAM Control Register                                                |     |

| Table 5-2. Example of Re-Mapping Relocatable RAM Memory                                    |     |

| Table 5-3. Word Write Operation Example (Original Data in Register $1 = 0x1234$ )          |     |

| Table 5-4. Long-Word Write Operation Example (Original Data in Register $1 = 0x12345678$ ) |     |

| Table 5-5. Summary of MOVEC Access-Based Registers                                         |     |

| Table 5-6. Source Function Code Register                                                   |     |

| Table 5-7. Destination Function Code Register                                              |     |

| Table 5-8. User Stack Pointer Register                                                     |     |

| Table 5-9. Vector Base Register                                                            |     |

| Table 5-10. Configuration Access Control Register                                          |     |

| Table 5-11. Memory Base Offset Register                                                    |     |

| Table 5-12. Memory and Register Group Address Map Table                                    |     |

| Table 5-13. Memory Protection Units                                                        |     |

| Table 5-14. MPU Block Control Base Register                                                | .91 |

| Table 5-15. MPU Block Control Attributes Register                   | 91  |

|---------------------------------------------------------------------|-----|

| Table 5-16. Value and Block Sizes                                   | 92  |

| Table 5-17. CTX MPU Allocation Register                             | 93  |

| Table 5-18. Example of MPU Data Space                               | 93  |

| Table 5-19. Example of MPU Protection                               | 94  |

| Table 5-20. Complete Register Address Map Table                     | 95  |

| Table 6-1. External Bus Interface Signal List                       | 130 |

| Table 6-2. External Bus Chip Select Control Register                | 131 |

| Table 6-3. Chip Select Timing Register                              |     |

| Table 6-4. External Bus Default Timing Register                     | 136 |

| Table 6-5. External Bus Priority Register                           | 137 |

| Table 6-6. Registers Used to Program the SDRAM Controller           | 138 |

| Table 6-7. SDRAM Timing Parameter 0 Register                        |     |

| Table 6-8. SDRAM Timing Parameter 1 Register                        | 140 |

| Table 6-9. SDRAM Configuration 0 Register                           | 140 |

| Table 6-10. SDRAM Configuration 1 Register                          | 142 |

| Table 6-11. SDRAM External Bank Configuration Register              | 143 |

| Table 6-12. SDRAM Module Types Address Mapping for 16-Bit Bus Width | 148 |

| Table 6-13. SDRAM Module Types Address Mapping for 8-bit Bus Width  |     |

| Table 6-14. SDRAM External I/O Signal List                          | 149 |

| Table 7-1. PMUChxy_Control                                          | 160 |

| Table 7-2. PMUChxy_Status                                           | 162 |

| Table 7-3. PMUChxy_PckXmitSize                                      | 163 |

| Table 7-4. PDMAChxy_PckRcvSize                                      | 163 |

| Table 7-5. PMUChxy_RcvFBufStart                                     | 164 |

| Table 7-6. PMUChxy_RcvFBufEnd                                       | 164 |

| Table 7-7. PMUChxy_XmitFBufStart                                    | 164 |

| Table 7-8. PMUChxy_XmitFBufEnd                                      | 165 |

| Table 7-9. PMUChxy_RcvFBufWrPtr                                     | 165 |

| Table 7-10. PMUChxy_RcvFBufRdPtr                                    | 166 |

| Table 7-11. PMUChxy_XmitFBufRdPtr                                   | 167 |

| Table 7-12. PMUChxy_XmitFBufWrPtr                                   | 167 |

| Table 7-13. PMUChxy_Xmit_Data                                       | 168 |

| Table 7-14. PMUChxy_Rcv_Data                                        | 168 |

| Table 7-15. GPIO_DIR_A                                              | 173 |

| Table 7-16. GPIO_DIR_B                                              | 174 |

| Table 7-17. PIO_DIR_C                                               | 175 |

| Table 7-18. GPIO_INV_A                                              | 176 |

| Table 7-19. GPIO_INV_B                                              | 177 |

| Table 7-20. GPIO_INV_C                                              | 178 |

| Table 7-21. GPIO_Data_A                                             | 178 |

| Table 7-22. GPIO Data B                                             | 179 |

| Table 7-23. GPIO_Data_C                                                   | 180 |

|---------------------------------------------------------------------------|-----|

| Table 7-24. ConfigRegA—Program Control                                    | 181 |

| Table 7-25. ConfigRegD—Master Control Register                            | 182 |

| Table 7-26. ConfigRegK—UIC Firmware ID                                    | 183 |

| Table 7-27. Firmware ID Codes                                             | 184 |

| Table 7-28. ConfigRegL—UIC Programming Checksum                           | 184 |

| Table 7-29. INTERRUPT_STATUS_REG                                          |     |

| Table 7-30. INTERRUPT_MASK_REG                                            | 185 |

| Table 7-31. DMAChx_Control                                                | 188 |

| Table 7-32. DMAChx_Source                                                 | 192 |

| Table 7-33. DMAChx_Destination                                            | 192 |

| Table 7-34. DMAChx_Count                                                  | 193 |

| Table 7-35. MAC Filter Mode Configuration Register                        | 196 |

| Table 7-36. MAC_Filter_Data_Write                                         | 198 |

| Table 7-37. MAC_Filter_Data_Read                                          | 198 |

| Table 7-38. MAC Filter HASH Table Partition 0                             | 199 |

| Table 7-39. MAC Filter HASH Table Partition 1                             | 199 |

| Table 8-1. Sequence Showing System Timer Interrupts_0 and _1 Enabled      | 202 |

| Table 8-2. Sequence Showing System Timer Interrupts_0, _1, and _2 Enabled | 203 |

| Table 8-3. System Timer Control Register                                  | 204 |

| Table 8-4. System Timer Prescale Register                                 | 205 |

| Table 8-5. System Timer Interrupt Control Register                        | 205 |

| Table 8-6. Watchdog Timer Control Register                                |     |

| Table 8-7. Watchdog Timer Reload Register                                 | 209 |

| Table 8-8. Examples of Frequencies Generated with the Timer Counter Unit  | 214 |

| Table 8-9. TCUx_Status                                                    | 214 |

| Table 8-10. TCUx_Mode                                                     | 215 |

| Table 8-11. Default Prescaler Settings                                    | 217 |

| Table 8-12. Clock Mode Values                                             | 217 |

| Table 8-13. TCUx_Counter                                                  | 218 |

| Table 8-14. TCUx_Chy_Mode                                                 | 218 |

| Table 8-15. Input Capture Mode Values                                     | 218 |

| Table 8-16. Output Compare Mode Values                                    | 219 |

| Table 8-17. TCUx_Chy_Input_Capture                                        |     |

| Table 8-18. TCUx_Chy_Output_Compare                                       | 221 |

| Table 8-19. ADC_ControlRegister                                           |     |

| Table 8-20. ADC_StartRegister                                             | 226 |

| Table 8-21. ADC Data Available Register                                   |     |

| Table 8-22. ADC Channel × Data Register                                   |     |

| Table 9-1. Debug-Feature Register Descriptions                            |     |

| Table 9-2. Debug Control Register                                         |     |

| Table 9-3. Debug Control Register Definition                              | 232 |

| Table 9-4. Debug Breakpoint and Watchpoint Registers                   | 234 |

|------------------------------------------------------------------------|-----|

| Table 9-5. Watchpoint Block Size and Break/Watch Mode Control Register | 234 |

| Table 9-6. Breakpoint Address/Watchpoint Base Address Register         |     |

| Table 9-7. Watchpoint Block Size and Break/Watch Mode Control Register | 237 |

| Table 9-8. Watchpoint Data Register                                    | 237 |

| Table 9-9. Watchpoint Data Mask Register                               | 237 |

| Table 9-10. Trace Control Register                                     | 238 |

| Table 9-11. Debug Trace Buffer Control Register                        | 238 |

| Table 9-12. Trace Buffer Base Address Register                         | 239 |

| Table 9-13. Call and Branch Instructions that Generate Address Strobes | 241 |

| Table 9-14. Example 1 of Debug-Feature Register Implementation         | 242 |

| Table 9-15. Example 2 of Debug-Feature Register Implementation         | 243 |

| Table 9-16. Example 3 of Debug-Feature Register Implementation         | 245 |

| Table 10-1. Summary of fido1100 Power-Saving Modes                     | 248 |

| Table 10-2. Power-On Reset Register                                    | 252 |

| Table 10-3. Clock Mask Register                                        | 253 |

| Table 11-1. Configuration Access Control Register                      | 255 |

| Table 12-1. Interrupt 'N' Control Registers (where N=07)               | 257 |

| Table 12-2. Faulted Context Register                                   | 258 |

| Table 12-3. Context Control Register                                   | 258 |

| Table 12-4. Context Timer Enable Register                              | 259 |

| Table 12-5. Context Timer Counter Register                             | 260 |

| Table 12-6. Context Maximum Time Register                              | 260 |

| Table 12-7. Context Timer Clear Register                               | 261 |

| Table 12-8. Context Idle Timer Register                                | 261 |

| Table 12-9. Context Claim Priority Inheritance Register                | 262 |

| Table 12-10. Pending Contexts Register                                 | 262 |

| Table 12-11. Claim Register                                            | 262 |

| Table 12-12. Software Interrupt Control Register                       | 262 |

| Table 12-13. Software Interrupt Actuation Register                     | 263 |

| Table 12-14. Relocatable RAM Control Register                          | 263 |

| Table 12-15. Configuration Access Control Register                     | 263 |

| Table 12-16. Memory Base Offset Register                               | 264 |

| Table 12-17. MPU Block Control Base Register                           | 264 |

| Table 12-18. MPU Block Control Attributes Register                     | 264 |

| Table 12-19. CTX MPU Allocation Register                               |     |

| Table 12-20. External Bus Chip Select Control Register                 |     |

| Table 12-21. Chip Select Timing Register                               |     |

| Table 12-22. External Bus Priority Register                            |     |

| Table 12-23. SDRAM Timing Parameter 0 Register                         |     |

| Table 12-24. SDRAM Timing Parameter 1 Register                         |     |

| Table 12-25. SDRAM Configuration 0 Register                            | 270 |

| Table 12-26. | SDRAM Configuration 1 Register             | 272 |

|--------------|--------------------------------------------|-----|

|              | SDRAM External Bank Configuration Register |     |

|              | PMUChxy_Control                            |     |

| Table 12-29. | PMUChxy_Status                             | 275 |

| Table 12-30. | PMUChxy_PckXmitSize                        | 276 |

| Table 12-31. | PDMAChxy_PckRcvSize                        | 277 |

| Table 12-32. | PMUChxy_RcvFBufStart                       | 277 |

| Table 12-33. | PMUChxy_RcvFBufEnd                         | 277 |

| Table 12-34. | PMUChxy_XmitFBufStart                      | 277 |

| Table 12-35. | PMUChxy_XmitFBufEnd                        | 278 |

| Table 12-36. | PMUChxy_RcvFBufWrPtr                       | 278 |

| Table 12-37. | PMUChxy_RcvFBufRdPtr                       | 278 |

| Table 12-38. | PMUChxy_XmitFBufRdPtr                      | 279 |

| Table 12-39. | PMUChxy_XmitFBufWrPtr                      | 279 |

| Table 12-40. | PMUChxy_Xmit_Data                          | 279 |

| Table 12-41. | PMUChxy_Rcv_Data                           | 280 |

| Table 12-42. | GPIO_DIR_A                                 | 280 |

| Table 12-43. | GPIO_DIR_B                                 | 281 |

| Table 12-44. | PIO_DIR_C                                  | 282 |

| Table 12-45. | GPIO_INV_A                                 | 282 |

| Table 12-46. | GPIO_INV_B                                 | 283 |

| Table 12-47. | GPIO_INV_C                                 | 284 |

| Table 12-48. | GPIO_Data_A                                | 285 |

| Table 12-49. | GPIO_Data_B                                | 286 |

|              | GPIO_Data_C                                |     |

| Table 12-51. | ConfigRegA—Program Control                 | 287 |

| Table 12-52. | ConfigRegD—Master Control Register         | 288 |

|              | ConfigRegK—UIC Firmware ID                 |     |

|              | ConfigRegL—UIC Programming Checksum.       |     |

|              | INTERRUPT_STATUS_REG                       |     |

|              | INTERRUPT_MASK_REG                         | 289 |

|              | DMAChx_Control                             | 290 |

|              | <del>-</del>                               | 293 |

|              | DMAChx_Destination                         |     |

|              | DMAChx_Count                               |     |

|              | MAC Filter Mode Configuration Register     |     |

|              | MAC_Filter_Data_Write                      |     |

|              | MAC_Filter_Data_Read                       |     |

|              | System Timer Control Register              |     |

|              | System Timer Prescale Register             |     |

|              | System Timer Interrupt Control Register    |     |

| Table 12-67. | Watchdog Timer Control Register            | 298 |

| Table 12-68.  | Watchdog Timer Reload Register                              | 299 |

|---------------|-------------------------------------------------------------|-----|

| Table 12-69.  | TCUx_Status                                                 | 299 |

| Table 12-70.  | TCUx_Mode                                                   | 300 |

| Table 12-71.  | TCUx_Counter                                                | 301 |

| Table 12-72.  | TCUx_Chy_Mode                                               | 302 |

| Table 12-73.  | TCUx_Chy_Input_Capture                                      | 303 |

|               | TCUx_Chy_Output_Compare                                     |     |

|               | ADC_ControlRegister                                         |     |

| Table 12-76.  | ADC_StartRegister                                           | 305 |

| Table 12-77.  | ADC Data Available Register                                 | 305 |

| Table 12-78.  | ADC Channel × Data Register                                 | 306 |

| Table 12-79.  | Debug Control Register Definition                           | 306 |

| Table 12-80.  | Watchpoint Block Size and Break/Watch Mode Control Register | 307 |

| Table 12-81.  | Breakpoint Address/Watchpoint Base Address Register         | 308 |

| Table 12-82.  | Watchpoint Data Register                                    | 308 |

| Table 12-83.  | Watchpoint Data Mask Register                               | 308 |

| Table 12-84.  | Debug Trace Buffer Control Register                         | 309 |

| Table 12-85.  | Trace Buffer Base Address Register                          | 310 |

| Table 12-86.  | Power-On Reset Register                                     | 310 |

| Table 12-87.  | Clock Mask Register                                         | 311 |

| Table 13-1. R | Pevision History                                            | 312 |

#### **CONVENTIONS**

**Arial Bold** Designates headings, figure captions, and table captions.

Blue Designates hyperlinks (PDF copy only).

Courier Designates code text.

Italics Designates emphasis or caution related to nearby information. Italics is also

used to designate variables, refer to related documents, and to differentiate terms from other common words (e.g., "If the *set* parameter is 0, then they will be

cleared.").

#### **NOMENCLATURE**

| ADC | Analog-to-Digital Converter. |

|-----|------------------------------|

|-----|------------------------------|

CMU Context Management Unit—Controls context switching based on context priorities.

DMA Direct Memory Access—Independent means of transferring data without CPU

intervention.

ISR Interrupt Service Routine—Code that will be executed when an exception or

interrupt is processed. Address of ISR is obtained from exception vector table for

the executing context.

MPU Memory Protection Unit—Provides access control to blocks of memory on a

context basis.

PMU Peripheral Management Unit—The fido1100 subsystem containing transmit and

receive frame buffers.

RREM Relocatable Rapid Execution Memory—Configurable internal instruction memory

used to speed up execution of critical sections of applications.

SDRAM Synchronous Dynamic RAM

SPIDER Software Profiling and Integrated Debug Environment—The fido1100 hardware

breakpoints, watchpoints, and trace features.

TCU Timer Counter Unit.

UIC Universal I/O Controller—Firmware controlled communication protocol engines.

URAM User RAM—Internal 24 Kbyte block of RAM available for use by applications.

WDT Watchdog Timer—Timer used to prevent runaway execution.

#### SAFETY INFORMATION

**DANGER** Certain applications using semiconductor products may involve potential risks of

death, personal injury, or environmental damage. To minimize the risks associated with end-user applications, adequate design and operating safeguards must be

provided by the customer to minimize inherent or procedural hazards.

**WARNING** Innovasic Semiconductor, Inc. (Innovasic), products are not designed, warranted,

or authorized for use in life-support devices or systems or in other critical applications. The inclusion of Innovasic products in such applications is fully at

the customer's risk.

**WARNING** Be aware of all hazards involved in handling electrical circuitry and be familiar

with practices for preventing accidents that may cause personal injury or death.

**CAUTION** Electrostatic discharge (ESD) can destroy or damage integrated circuits and

semiconductor devices. When working near or handling these components, ensure that proper ESD suppression measures are taken. Additionally, do not store or ship

these components near strong electrostatic, electromagnetic, magnetic, or

radioactive fields.

#### **PREFACE**

This document describes the capabilities, operation, and programming of the fido1100<sup>TM</sup> communications controller. The organization and content of this document are as follows:

- Chapter 3, Context Architecture—An introduction to the fido1100 multiple hardware contexts concept.

- Chapter 4, Core CPU—Covers the Execution Unit, register model and data types, exception processing, and details of the multiple hardware contexts operation.

- Chapter 5, Memory Management and Protection—Description of the Memory Protection Unit features of the fido1100 and the Relocatable Rapid Execution Memory. Introduces the programmable Chip Select registers. Also includes a Register Map quick reference of the fido1100, sorted by address.

- Chapter 6, External Bus Interface—Details of the programmable chip-select registers and the SDRAM Controller and its registers. Covers how external bus arbitration can be used to connect the fido1100 on a shared address/data bus.

- Chapter 7, Peripheral Management Unit—Details the operation and registers of the PMU subsystem in the fido1100. Covers the transmit and receive buffer functions of the PMU. Describes how to load a UIC with firmware. Details the two channels of DMA operation and how to use the DMA in conjunction with the PMU to offload the CPU for data transmit and receive functions. The MAC Filter section details the usage of the programmable MAC address filter table.

- Chapter 8, Internal Peripherals—Details the System Timer, Timer Counter Units, Watchdog Timer and Analog-to-Digital Converter in the fido1100.

- Chapter 9, Debug Features—Covers the debug, trace and breakpoint features of the fido1100. The JTAG debug interface, hardware breakpoints and watchpoints, and tracing are illustrated by examples.

- Chapter 10, Power Control—Describes how to control the power to the fido1100 internal peripherals and the LPSTOP and STOP instructions.

- Chapter 11, Access Controlled Registers—Details the fido1100 mechanism for limiting access to registers or bit fields in register to the Master Context only. Access control is used to protect sensitive fields or settings controlled by registers.

- Chapter 12, Register Map Reference—Presents all the fido1100 registers organized by function peripheral with descriptions of the bit fields in the registers.

#### 1. Introduction to fido1100 Architecture

Innovasic Semiconductor's fido1100 is the first product in the fido™ family of real-time communications controllers. The fido communications controller architecture is uniquely optimized for solving memory bottlenecks, and is designed from the ground up for deterministic processing. Critical timing parameters, such as context switching and interrupt latency, are precisely predictable for real-time tasks. The fido1100 also incorporates the Universal I/O Controller (UIC™) that is configurable to support various communication protocols across multiple platforms. This flexibility relieves the designer of the task of searching product matrices to find the set of peripherals that most closely match the system interface needs. The Software Profiling and Integrated Debug EnviRonment (SPIDER™) has extensive real-time code debug capabilities without the burden of code instrumentation.

#### 1.1 Features

The fido1100 communications controller's features include:

- A real-time 32-bit microcontroller

- CISC architecture optimized for real time

- CPU32+ (Motorola® 68000) instruction-set compatible

- Five hardware contexts, each with its own register set and interrupt vector table

- An 8- or 16-bit external bus interface with programmable chip selects

- 24 Kbytes of high-speed internal user SRAM

- 32 Kbytes of high-speed internal user-mappable Relocatable Rapid Execution Memory (RREM)

- A Memory Protection Unit

- An SDRAM controller

- Flat, contiguous memory space

- A non-aligned memory access

- A dedicated Peripheral Management Unit (PMU)

- Four Universal I/O Controllers (UICs) capable of supporting the following protocols:

- GPIO

- 10/100 Ethernet with flexible MAC Address Filtering schemes

- EIA-232

- CAN

- SPI

- $I^2C^{TM}$  Bus

- SMBus

- HDLC

- Two channels of full-featured direct memory access (DMA) with deterministic arbitration

- Two Timer/Counter Units (TCU)

- A Watchdog timer, system timer, and context timers

- JTAG emulation and debug interface

- Standard 208 PQFP, TQFP, and BGA packaging

- 3.3V operation with 5V-tolerant I/O

- Industrial temperature grade

- Software development supported by libraries and tools including UIC firmware for various interface protocols and formats, as well as a customized GNU tool set.

# 1.2 Architectural Overview

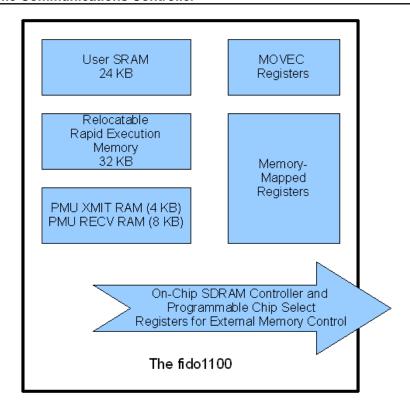

A diagram of the fido1100 communications controller is shown in Figure 1-1. Brief descriptions of the major architectural components are provided in the following subsections.

#### 1.2.1 Core CPU

The fido1100 includes a 32-bit CPU featuring Complex-Instruction-Set-Computer (CISC) architecture optimized for real time. The Motorola®-CPU32-instruction-set compatible CPU contains the following subsystems:

- Execution Unit—A single unit that handles all instruction fetch and execution for all contexts.

- Context Management Unit—Handles context priorities and when a context switch is required.

- Exception Handling (Interrupts and Faults)—Determines priorities of interrupts and handles processing of interrupts (detailed in later sections).

Figure 1-1. Diagram of the fido1100 Communications Controller

#### 1.2.2 Memory Management

- Relocatable Rapid Execution Memory (RREM)—Internal 32-Kbyte memory that can be used as an instruction source for code that requires maximum execution speed.

- Memory Protection Unit (MPU)—Access-control method for 16 user-configurable blocks of internal or external memory on a context basis. A block of memory may be inaccessible, read only or read/write accessible to a selectable set of contexts. The MPU provides the space partitioning needed in deterministic, real-time systems.

#### 1.2.3 External Bus Interface

The interface to all external memory. It handles memory interface timing and arbitration of external bus requests. The external bus interfaces provide all address, data, and control line to

implement either an 8- or 16-bit microcontroller system bus. Additional details on the characteristics, operation, and timing of the external bus interfaces are provided in Chapter 6, External Bus Interface.

- Address/data bus

- 31-bit address bus to access up to 2 Gbytes of memory space

- 8- or 16-bit data bus

- Chip Selects—Eight programmable chip selects with programmable size, data width, and timing.

- SDRAM Controller—Supports 8- or 16-bit data interfaces to SDRAM.

- External Bus Arbitration—The fido1100 provides signals to allow it to operate in a multibus master environment.

#### 1.2.4 PMU/UIC/CPU DMA

The PMU, UIC, and CPU DMA work together as a fast data transport scheme that requires minimal Core CPU overhead or intervention.

- Peripheral Management Unit (PMU)—A set of user-configurable buffers for data transmission and reception via the UICs.

- Universal Input/Output Controller (UIC)—Programmable protocol engine

- CPU DMA—Two independent channels of DMA for data transfer

#### 1.2.5 Internal Peripherals

The fido1100 incorporates the following set of internal peripherals:

- Two Timer Counter Units (TCU)—Additional details on the characteristics, operation, and timing are provided in Section 8.3, Timer Counter Units.

- Analog-to-Digital Converter (ADC)—The characteristics, operation, and timing of the 10-bit, 8-channel ADC are provided in Section 8.4, Analog-to Digital Converter.

- Power Control—Internal peripherals can be put into a low-power consumption mode. Detailed information can be found in Chapter 10, Power Control.

# 1.2.6 JTAG/Debug

The JTAG Interface is used for controlling the SPIDER (see Chapter 9, Debug Features).

- Breakpoints—Eight hardware context-aware breakpoints that can be chained to set up if/then triggering conditions.

- Watchpoints—Eight hardware watchpoints.

- Trace—Follow program execution with trace buffers.

- Debug Control—Hardware single-step and context status control.

- Statistical Profiling—SPIDER provides statistical software profiling to identify critical pieces of code.

# 1.3 Programming Model

# 1.3.1 CPU32 Instruction Set Compatible

The fido1100 supports the CPU32 instruction set with some modifications, and has some new instructions (see Chapter 4, Core CPU, and *The fido1100 Instruction Set Reference Guide* for details). The fido1100 general instruction classes include machine functions for all of the following operations:

- Data movement

- Arithmetic operations

- Logical operations

- Shifts and rotates

- Bit manipulation

- Binary-Coded Decimal (BCD) arithmetic

- Program control

- System control

- Power control

#### 1.3.2 Memory-Mapped Address Space

• Address and data space (31-bit address space and 32-bit data paths internally, 16-bit data path externally)

- Supports byte (8-bit), word (16-bit), long-word (32-bit), and quad-word (64-bit) operations

- Supports non-aligned accesses to memory

- Selectable little-endian or big-endian accesses to memory

# 2. Programmer Reference Overview

#### 2.1 User Guide Structure

This User Guide presents procedures for designing and programming a system using the fido1100 communications controller. Detailed information about the fido1100 CPU, internal peripherals, context management, and exception processing is provided.

The guide is divided into chapters that present the following topics:

- Core CPU (Chapter 3 and Chapter 4)

- Context Management

- Execution Unit

- Exception Handling (Interrupts and Faults)

- Memory Management (Chapter 5)

- RREM (Relocatable Rapid Execution Memory)

- MPU (Memory Protection Unit)

- External Bus Interface (Chapter 6)

- Address/Data bus

- Programmable Chip Selects

- SDRAM Controller

- External Bus Arbitration

- PMU/UIC/CPU DMA (Chapter 7)

- PMU (Peripheral Management Unit)

- UIC (Universal I/O Controller)

- CPU DMA

- MAC Filter

- Internal Peripherals (Chapter 8 and Chapter 10)

- TCU (Timer Counter Units)

- ADC (Analog-to-Digital Converter)

- Power Control

- JTAG/Debug (Chapter 9)

- Breakpoints

- Watchpoints

- Trace

- Debug Control/Status Registers

# 2.2 Chapter Overview

- Chapter 3, Context Architecture—An introduction to the fido1100 multiple hardware contexts concept.

- Chapter 4, Core CPU—Covers the Execution Unit, register model and data types, exception processing, and details of the multiple hardware contexts operation.

- Chapter 5, Memory Management and Protection—Description of the Memory Protection Unit features of the fido1100 and the Relocatable Rapid Execution Memory. Introduces the programmable Chip Select registers. Also includes a Register Map quick reference of the fido1100, sorted by address.

- Chapter 6, External Bus Interface—Details of the programmable chip-select registers and the SDRAM Controller and its registers. Covers how external bus arbitration can be used to connect the fido1100 on a shared address/data bus.

- Chapter 7, Peripheral Management Unit—Details the operation and registers of the PMU subsystem in the fido1100. Covers the transmit and receive buffer functions of the PMU. Describes how to load a UIC with firmware. Details the two channels of DMA operation and how to use the DMA in conjunction with the PMU to offload the CPU for data transmit and receive functions. The MAC Filter section details the usage of the programmable MAC address filter table.

- Chapter 8, Internal Peripherals—Details the System Timer, Timer Counter Units, Watchdog Timer and Analog-to-Digital Converter in the fido1100.

- Chapter 9, Debug Features—Covers the debug, trace and breakpoint features of the fido1100. The JTAG debug interface, hardware breakpoints and watchpoints, and tracing are illustrated by examples.

- Chapter 10, Power Control—Describes how to control the power to the fido1100 internal peripherals and the LPSTOP and STOP instructions.

- Chapter 11, Access Controlled Registers—Details the fido1100 mechanism for limiting access to registers or bit fields in register to the Master Context only. Access control is used to protect sensitive fields or settings controlled by registers.

- Chapter 12, Register Map Reference—Presents all the fido1100 registers organized by function peripheral with descriptions of the bit fields in the registers.

# 3. Context Architecture

#### 3.1 Introduction

One way to gain a better understanding of the fido context architecture is to view it from the perspective of a standard microprocessor—for example, a CPU32. A standard CPU32 can be viewed as a single hardware context, with a standard set of registers. Interrupts and other peripheral inputs are handled and processed as required by the microprocessor execution engine. Whenever an interrupt occurs, priority/masking willing, the currently executing task is stopped, stack operations occur, the interrupt is processed as required by the handler and the task execution resumes.

In a multi-task software application, any task switch will have the overhead of caching and decaching registers for tasks to be saved/resumed. A faulting task will typically be suspended by an OS (if one exists) or can even halt a system, requiring a reset or restart to recover the system (see Figure 3-1).

Figure 3-1. Standard Microprocessor, Single Context View

A discussion of the fido1100 architecture implementation follows.

The fido1100 implements five independent hardware contexts. Each has its own stack, register set, and additional registers for context control and operation. Each interrupt in the system is "associated" with a given context (details are provided in later chapters). Each context and each interrupt has a priority mechanism used by the hardware execution unit to facilitate operation.

With fido, a true multi-tasking system is possible with or without an OS, and task-switching times are greatly reduced and can be "deterministic" based on context type (see Section 4.8, Context Management). No caching of registers to memory is ever needed or used to switch contexts.

In fido, a faulting event is isolated to a given context, protecting the remaining system that can continue to run. A faulting task can be reset or quickly re-started if desired, which of course is application dependent (see Figure 3-2).

A discussion of the different context types and their modes of operation follows.

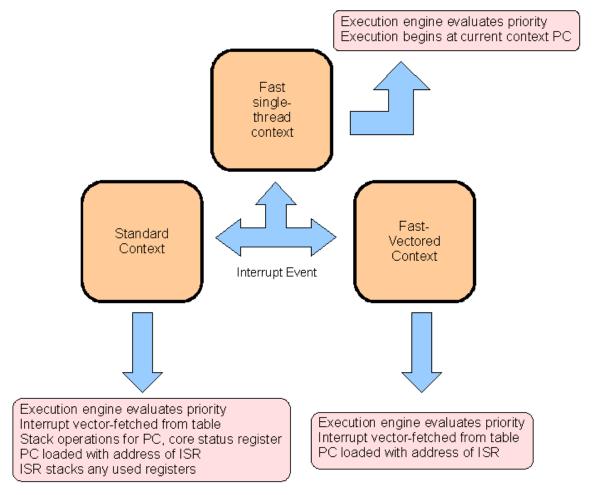

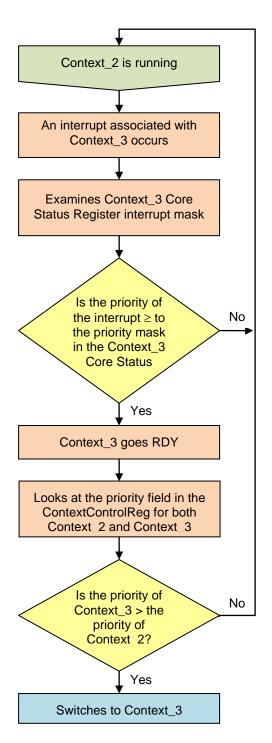

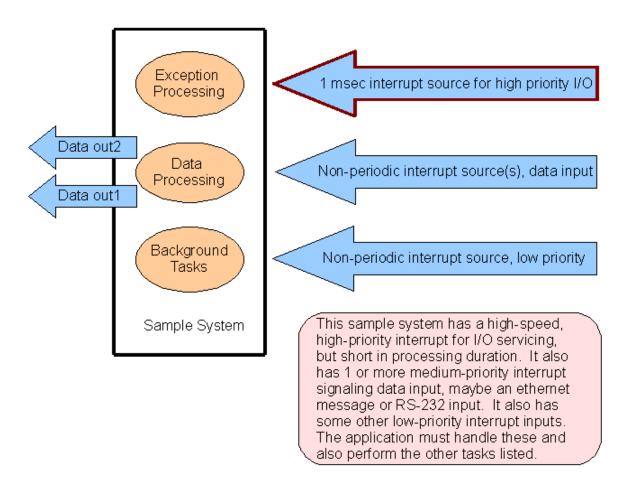

### 3.2 Context Types and Operational Modes

There are three types of fido contexts: Standard, Fast-Vectored, and Fast Single-Thread (FST). The context type determines both context behavior and switching time. Each context has an assigned priority, can have interrupts associated with it, and includes such features as time slicing. Although contexts can be completely isolated from one another, they can communicate and share resources. Interrupts are inextricably coupled to contexts in that any interrupt in the system is associated with only one context. Each context has three possible states, ready (RDY), not ready (NOT\_RDY), and halted. The fido pioneers a new "sleep" instruction to manage these states. The sleep instruction can change the state of any context from RDY to NOT\_RDY. This mechanism interrupts the CPU to allow another context to run (see Figure 3-3).

#### 3.2.1 Standard Context

The standard context retains standard, single-context operational compatibility. If code is executing in a standard context and an interrupt associated with this context occurs, the interrupt is handled in the usual manner. The interrupt service routine address is fetched from the vector table and if the interrupt is of higher priority than the context, the current PC and status register are stacked then re-loaded from the vector table. The handler (which needs to PUSH/POP any registers it uses) is then called, executes, performs an interrupt return, the PC and status register are unstacked, and the code resumes where it left off.

#### 3.2.2 Fast-Vectored Context

The fast context is really an interrupt handler that operates as a context. If an interrupt occurs that is associated with a Fast Context, the PC for that context is loaded from the vector table, and execution begins. No stack operations occur except those needed by the context itself. It runs to completion then sleeps itself. Since a Fast Context loads the PC with the ISR address from the vector table, any number of interrupts can be associated with a context of this type. The context switch time for a Fast Context is only the time it takes to load the PC and begin.

Figure 3-2. The fido1100 Multi-Context View

Figure 3-3. Context Types and State Transitioning

# 3.2.3 Fast Single-Thread Context

The FST context is really a single thread that operates as a context. If an interrupt occurs that is associated with a FST context, execution begins immediately at the current PC for that context. No vector-table access or stacking occurs. The FST type of context must be coded to terminate using a sleep/branch combination to ensure the PC for the context is always where the context should begin execution the next time the interrupt occurs. The context switch time for a FST context is near single cycle. Applications for this type of context include situations where high priority, minimal response time I/O, or high frequency events must be handled in the system (see Figure 3-4).

Figure 3-4. Context Interrupt Overhead

#### 3.3 Master Context

Context\_0 is the Master Context and it holds special powers. By default, it is the highest priority context regardless of priority settings for other contexts. Only code running in Context\_0 can write to every fido register, including the context control register of every context. By default, the fido powers up by running in Context\_0. A recommended practice is to house all initialization code here, set up all other contexts according to application needs, then sleep Context\_0 and use it to handle exceptions from all other contexts.

Many applications can run entirely in Context\_0, which is perfectly acceptable. After Context\_0, the priorities of the other contexts are assignable through registers. However, if both Context\_1 and Context\_4 are assigned a priority of six for example, Context\_1 will have the higher priority.

Many fido registers have access-controlled bit fields (discussed in later chapters). Only Context\_0 can write to access-controlled bit fields, and only while in supervisor mode. This restriction

prevents program corruption—a safety feature that keeps order (and limits chaos) in this multi-threaded, real-time embedded application running on a very flexible machine.

# 3.4 Summary

There are no other real rules or restrictions for context usage, understanding the chip's flexibility and how it works is the key to implementing the application.

- Any or all of the five fido contexts can be used by an application.

- Unused contexts are disabled and have no affect on system operation.

- In review, contexts have three states (HALTED, RDY, and NOT\_RDY). A HALTED state will not run (that is, the hardware execution engine will bypass it for scheduling consideration) without master Context\_0 writing to the context control register or JTAG intervention.

- When a context is done (temporarily), the SLEEP instruction is used to transition from a RDY to the NOT RDY state.

- All interrupts have an association to a context and a priority relative to that context.

- If a context is set up as a Fast Single-Thread context, any interrupt associated with that context will cause the context to execute the code indicated by the context's PC.

- For a Fast context, any interrupt associated with that context will immediately cause the context to execute the Interrupt Service Routine defined by the context's vector exception table.

- Certain registers and the access-controlled field in all registers are writable by only the Master Context, Context\_0.

Chapters herein will discuss the use of context timers, time-slicing, memory protection, claim registers, and the use of internal peripherals and other features of fido. These are closely related to context management, and are typically set up by the Master Context during initialization based on application needs. See Section 4.8, Context Management, for details.

#### 4. Core CPU

#### 4.1 Overview

The core CPU is the main computer in the chip. The fido1100 core is based on the CPU32 architecture, and is compatible with the CPU32 instruction set. Some exceptions will be listed in this chapter. All contexts share the same Execution Unit, which is the portion of the Core CPU that fetches, decodes, and executes instructions. However, as introduced in Chapter 3, Content Architecture, each of the five hardware contexts in the fido1100 has its own register set. This unique feature of fido allows it to operate as five machines in one where the application is concerned.

The following features of the fido1100 are discussed in this section:

- Address and Data Space (32-bit address space and 32-bit data paths)

- Byte, word (16-bit), long-word (32-bit), and quad-word (64-bit) operations

- Register Model

- User/Supervisor Space

- Instruction Set Summary

- Interrupts, Faults, and Exceptions

- External Interrupts

- Interrupt Priorities and Control

- Interrupt, Fault, and Exception Handling

- Short Format Stack Frames

- Instruction Error Stack Frame

- o Fault and Exception Handling

- Reset Processing

- Context Management

Other internal features of the fido1100 (the PMU, Internal SRAM, the RREM, Memory Protection Unit [MPU], SDRAM controller, and External Bus Interface) are discussed in subsequent chapters.

#### 4.2 Address and Data Space

The fido1100 internal address and data bus are 32-bits wide. It supports the following data types:

- Data types

- BCD—4-bit representation (supported by certain instructions)

- Byte—8-bit signed and unsigned representations

- Word—16-bit signed and unsigned representations

- Long-word—32-bit signed and unsigned representations

- Quad-word—64-bit signed and unsigned representations (supported by certain instructions, requires a register pair to contain data)

The fido1100 supports an extensive set of addressing modes for source and destination operands of an instruction.

- Memory addressing modes

- Dn—Data Register

- An—Address Register

- (An)—Address Register Indirect

- (An)+—Address Register Indirect with post-increment

- -(An)—Address Register indirect with pre-decrement

- (d16,An)—Address Register Indirect with displacement

- (d8,An,Xn.Size\*Scale)—address Register indirect with displacement and scaling

- (bd,An,Xn.Size\*Scale)—address Register indirect with displacement and scaling

- (d16,PC)—Program Counter relative with displacement

- (d8,PC,Xn.Size\*Scale)—Program Counter relative with displacement and scaling

- (bd,PC,Xn.Size\*Scale)—Program Counter relative with displacement and scaling

- (xxx).W—memory pointer

- (xxx).L—memory pointer

- #xxx—immediate

An important fido1100 feature to be remembered is that the most significant bit (Bit [31]) of the address is used for Endian Mode Control. This limits the fido1100 to two Gbytes of space as opposed to four Gbytes of space. See Chapter 5, Memory Management and Protection, for details on Endian Mode Control.

The external address bus of the fido1100 is 31 bits and the external data bus is 16 bits. The external interface of the fido1100 is discussed in Chapter 6, External Bus Interface.

#### 4.3 Register Model

In the fido1100, each hardware context has its own set of registers. These registers are writable by only the context to which they belong, and by the master context. The register set summary is as follows:

- Eight 32-bit User Data Registers (D0-D7)

- Seven 32-bit Address Registers (A0-A6)

- Two 32-bit Stack Pointers (A7 and A7')

- The two stack pointers are indexed by supervisor status (A7' stack pointer for supervisor mode, and A7 for user mode)

- One 32-bit Program Counter

- One 16-bit Status Register (SR)

- One 32-bit Vector Base Register (VBR)

- Two 3-bit Alternate Function Registers (SFC, DFC)

For the internal address of these registers, refer to the Memory and Register Group Address Map Table in Chapter 5.

The fido1100 architecture uses the big-endian format (i.e., the most significant bytes are stored at the lowest addresses). For internal data representation, formats are used as described in the following sections.

# 4.3.1 Data Register Operands

- Each data register is 32 bits wide.

- Byte operands occupy the low-order 8 bits, word operands occupy the low-order 16 bits, and long-word operands occupy the full 32 bits.

- When a data register is used as either a source or destination operand (byte or word), only

the low-order byte or word is changed; the high-order portion is not used and is left

unchanged.

- Operands in data registers can represent a single byte, a 16-bit word, a 32-bit long word, or a 64-bit quad word.

- Quad-word data can consist of any two data registers without restrictions on order or pairing.

- Quad words result from 32-by-32 multiply or divide operations.

- There are no explicit instructions for manipulating quad-word data types.

- For signed operations, standard 2's complement notation is used.

- Instructions requiring BCD operands use the low-order byte as two packed BCD digits.

#### 4.3.2 Address Register Operands

- Each address register is 32 bits wide.

- Address registers cannot be used for byte-sized operands.

- Either the low-order word or the entire 32 bits are used as a source operand. When used as a word-sized source operand, the 16-bit word is sign-extended to 32 bits before being used.

- As a destination operand, the entire register is affected regardless of operation size.

#### 4.3.3 Operands in Memory

- Memory is byte addressable.

- Multi-byte data is stored in big-endian format.

- Non-aligned access support:

- Accessing word- or long-word-sized operands does not require that the operand be word aligned or long-word aligned. Accessing this type of operand on an odd address will not result in an address exception.

#### 4.4 User/Supervisor Space

Context applications can be run in either User Mode or Supervisor Mode. Privileged instructions can be executed only in Supervisor mode. This mode control is set via the Status Register (SR).

The SR contains condition codes, the interrupt priority mask, the supervisor/user state, and trace enable. Only the Condition codes (lower 8 bits) are manipulated by user-mode instructions. When in supervisor mode, the entire register can be manipulated. Each context has its own copy of the status register. The SR is defined in Section 4.6.3, Interrupt Priorities and Control.

Separate stacks (as defined by A7 and A7') are used in User and Supervisor mode.

#### 4.5 Instruction Set Summary

The fido1100 supports the CPU32 instruction set with some modifications, and has some new instructions. The fido1100 general instruction classes include machine functions for all of the following operations:

- Data movement

- Arithmetic operations

- Logical operations

- Shifts and rotates

- Bit manipulation

- Binary-Coded Decimal (BCD) arithmetic

- Program control

- System control

- Power Control

Following is a discussion of each instruction class. The complete instruction set is provided in *The fido1100 Instruction Set Reference Guide*.

### 4.5.1 Data Movement Instructions

The MOVE instruction is the basic means of transferring and storing address and data. MOVE instructions transfer byte, word, and long-word operands from memory to memory, memory to register, register to memory, and register to register. Address movement instructions (MOVE or MOVEA) transfer word and long-word operands and ensure that only valid address manipulations are executed.

In addition to the general MOVE instructions, there are several special data movement instructions: move multiple registers (MOVEM), move peripheral data (MOVEP), move quickly (MOVEQ), exchange registers (EXG), load effective address (LEA), push effective address (PEA), link stack (LINK), and unlink stack (UNLK).

### 4.5.2 Integer Arithmetic Operations

The arithmetic operations include the four basic operations of add (ADD), subtract (SUB), multiply (MUL), and divide (DIV) as well as arithmetic compare (CMP, CMPM, CMP2), clear (CLR), and negate (NEG). *The fido1100 Instruction Set Reference Guide* includes ADD, CMP, and SUB instructions for both address and data operations with all operand sizes valid for data operations. Address operands consist of 16 or 32 bits. The clear and negate instructions apply to all sizes of data operands.

Signed and unsigned MUL and DIV instructions include:

- Word multiply to produce a long-word product

- Long-word multiply to produce a long-word or quad-word product

- Division of a long-word dividend by a word divisor (word quotient and word remainder)

- Division of a long-word or quad-word dividend by a long-word divisor (long-word quotient and long-word remainder)

A set of extended instructions provides multi-precision and mixed-size arithmetic. These instructions are add extended (ADDX), subtract extended (SUBX), sign extend (EXT), and negate binary with extend (NEGX).

## 4.5.3 Logic Instructions

The logical operation instructions (AND, OR, EOR, and NOT) perform logical operations with all sizes of integer data operands. A similar set of immediate instructions (ANDI, ORI, and EORI) provide these logical operations with all sizes of immediate data. The TST instruction arithmetically compares the operand with zero, placing the result in the condition code register.

#### 4.5.4 Shift and Rotate Instructions

The arithmetic shift instructions, ASR and ASL, and logical shift instructions, LSR and LSL, provide shift operations in both directions. The ROR, ROL, ROXR, and ROXL instructions perform rotate (circular shift) operations, with and without the extend bit. All shift and rotate operations can be performed on either registers or memory.

Register shift and rotate operations shift all operand sizes. The shift count may be specified in the instruction operation word (to shift from one to eight places) or in a register (modulo 64-shift count).

Memory shift and rotate operations shift word-length operands only one bit position. The SWAP instruction exchanges the 16-bit halves of a register. Performance of shift/rotate instructions is enhanced so that use of the ROR and ROL instructions with a shift count of eight allows fast byte swapping.

### 4.5.5 Bit Manipulation Instructions

Bit manipulation operations are accomplished using the following instructions: bit test (BTST), bit test and set (BSET), bit test and clear (BCLR), and bit test and change (BCHG). All bit manipulation operations can be performed on either registers or memory. The bit number is specified as immediate data or in a data register. Register operands are 32 bits long. Memory operands are 8 bits long.

#### 4.5.6 Binary-Coded Decimal Instructions

Five instructions support operations on Binary-Coded Decimal (BCD) numbers. The arithmetic operations on packed BCD numbers are add decimal with extend (ABCD), subtract decimal with extend (SBCD), and negate decimal with extend (NBCD).

# 4.5.7 Program Control Instructions

A set of subroutine call and return instructions and conditional and unconditional branch instructions perform program control operations.

# 4.5.8 System Control Instructions

Privileged instructions, trapping instructions, and instructions that use or modify the condition code register provide system-control operations. All of these instructions cause the processor to flush the instruction pipeline.

#### 4.5.9 Power Control Instructions

For a complete understanding of how STOP and LPSTOP instructions are implemented, see Chapter 10, Power Control.

## 4.5.10 Modifications to CPU32 Instruction Compatibility

This section discusses the modifications to the instructions the fido1100 implements differently from the CPU32.

- Interpolate—This causes an Illegal Instruction exception in the fido1100

- Table—This causes an Illegal Instruction exception in the fido1100

- MOVEC instruction—These are new control codes to define fido1100-specific registers

- LPSTOP and BKPT instructions

- Because the fido1100 exception handling is different from that of a CPU32, LPSTOP does not "export" interrupt priority via external-bus interface. See Chapter 10, Power Control, for more information.

- BKPT does not require or generate an external bus cycle for breakpoint acknowledge.

See Chapter 9, Debug Features, for more information.

- BGND—The fido1100 does not have a CPU32-style Background Debug Mode (BDM). The BDM instruction just executes a trap.

- Branch and Jump instructions have additional profiling support. (See Chapter 9, Debug Features, for details on call and branch trace capability.)

- Bcc

- BRA

- BSR

- Dbcc

- JMP

- JSR

- RTE

- RTS

- Table Lookup and Interpolate instructions are not implemented—they will TRAP instead. The fido1100 tools will issue a warning if these instructions are used in assembly code.

- TBLS and TBLSN

- TBLU and TBLUN

#### 4.5.11 New Instructions

This section discusses new instructions the fido1100 implements to support the multiple-hardware context architecture.

- SLEEP instruction:

- Similar to STOP but does not alter the SR and only affects the current context. Sleep causes the current context to change from the Ready (RDY) state to the Not Ready (NOT\_RDY) state allowing other pending contexts to run. See Section 4.9, Context Management, for complete details.

- TRAPX instruction

- Sends a trap signal to Master Context\_0. Can be used for inter-context communication and exception escalation.

#### 4.6 Interrupts, Faults and Exceptions

#### 4.6.1 Overview

This section presents the following:

- External Interrupts

- Interrupt Priorities and Control

- Interrupt, Fault, and Exception Processing

- Stack Frames

- Vector Table