### **General Description**

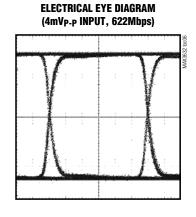

The MAX3632 burst-mode limiting amplifier is designed specifically for 622Mbps or 1244Mbps GPON (G.984) optical line terminal (OLT) receiver applications. Together with the MAX3630/MAX3631 burst-mode transimpedance amplifiers (TIAs), a wide-dynamic-range burst-mode signal current (from a PIN or avalanche photodiode) can be translated to a differential LVPECL output. The MAX3632 has an electrical input sensitivity of 4mV<sub>P-P</sub> that supports GPON class-B optical sensitivity at 622Mbps with a PIN photodiode. An LVPECL-compatible burst reset input (RST) connected to the limiting amplifier is used to control the offset correction loop of the MAX3632 as required for burst-mode operation, as well as to arm the threshold-setting circuitry of MAX3630/MAX3631 TIAs.

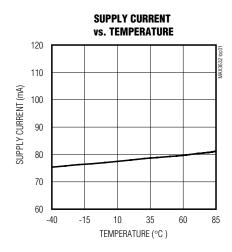

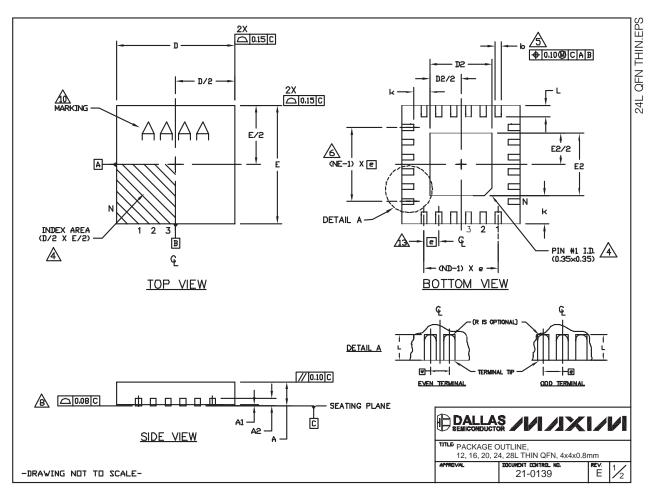

The MAX3632 is available in a low-profile, 4mm x 4mm, 24-lead thin QFN package. It operates from a single +3.3V power supply over a -40°C to +85°C temperature range.

#### **Applications**

622Mbps GPON OLT Receivers 1244Mbps GPON OLT Receivers

#### **Features**

- **♦ DC-Coupled Limiting Amplifier for Burst-Mode GPON Applications**

- ♦ Operates with Maxim's Burst-Mode Transimpedance Amplifier (MAX3630/MAX3631)

- **♦ LVPECL Data Output**

- ♦ 4mV<sub>P-P</sub> Input Sensitivity

- **♦ LVPECL Reset Input (RST)**

- **♦ LVPECL HOLD Input for Optional Control Modes**

- ♦ 4mm x 4mm TQFN Package

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |  |

|------------|----------------|-----------------|-------------|--|

| MAX3632ETG | -40°C to +85°C | 24 Thin QFN     | T2444-4     |  |

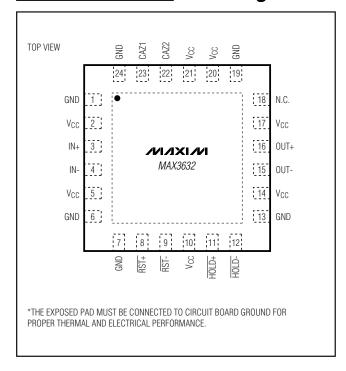

Pin Configuration appears at end of data sheet.

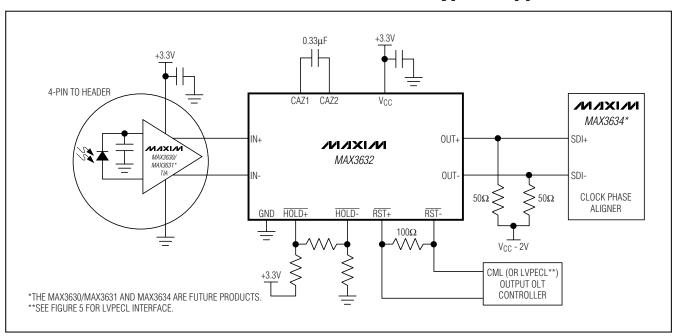

### **Typical Application Circuit**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Power-Supply Voltage (V <sub>CC</sub> )0.5V to +4.5V  | Operating Junction Temperature Range40°C to +125°C |

|-------------------------------------------------------|----------------------------------------------------|

| Voltage at IN+, IN-, RST-, RST+, HOLD+, HOLD-,        | Storage Temperature Range55°C to +150°C            |

| CAZ1, CAZ20.5V to (V <sub>CC</sub> + 0.5V)            | Lead Temperature (soldering 10s)+300°C             |

| LVPECL Output Current (OUT+, OUT-)50mA                |                                                    |

| Continuous Power Dissipation ( $T_A = +85^{\circ}C$ ) |                                                    |

| Derate 20.8mW/°C above +85°C1354mW                    |                                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values at } V_{CC} = +3.3 \text{V}, V_{IN} = 4 \text{mVp-p}, \text{ and } T_{A} = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Input (IN+, IN-) terminated with 100 $\Omega$  resistors to V<sub>CC</sub>.) (Note 1)

| PARAMETER                             | SYMBOL                                  | CONE                              | MIN T                                       | YP MAX                    | UNITS                  |                   |

|---------------------------------------|-----------------------------------------|-----------------------------------|---------------------------------------------|---------------------------|------------------------|-------------------|

| GENERAL SPECIFICATIONS                |                                         | 1                                 |                                             | 1                         |                        | 1                 |

| Data Rate                             |                                         |                                   |                                             |                           | 22,<br>244             | Mbps              |

| Power-Supply Current                  | Icc                                     | (Note 2)                          |                                             | 8                         | 30 100                 | mA                |

| Low-Frequency Cutoff                  |                                         |                                   |                                             |                           | 30                     | kHz               |

| CAZ Leakage Current                   |                                         |                                   |                                             |                           | 25                     | nA                |

| Power-Supply Noise Rejection          | PSNR                                    | f ≤ 10MHz (Note 3)                |                                             |                           | 24                     | dB                |

| INPUT SPECIFICATIONS (IN+, IN-        | -)                                      |                                   |                                             |                           |                        |                   |

| Minimum Input Offset Tolerance        | Minimum Input Offset Tolerance (Note 1) |                                   |                                             |                           | 5                      | mV                |

| Input Resistance                      | RIN                                     | Differential                      | 168                                         | 232                       | Ω                      |                   |

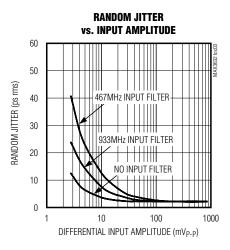

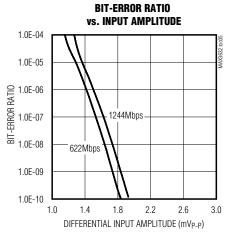

| Input Sensitivity                     |                                         | BER = $10^{-10}$ , $2^{23}$ -1 PR | RBS                                         |                           | 2                      | mV <sub>P-P</sub> |

| <b>OUTPUT SPECIFICATIONS (OUT</b>     | +, OUT-)                                |                                   |                                             |                           |                        |                   |

| Random Jitter (Notes 1, 4, 5)         | RJ                                      | 622Mbps                           | 2                                           | 28 40                     | DCD140                 |                   |

| Trandom sitter (Notes 1, 4, 5)        | HU                                      | 1244Mbps                          | -                                           | 18 22                     | psrms                  |                   |

| Deterministic Jitter (Notes 1, 4, 6)  | DJ                                      | 622Mbps                           | -                                           | 14 30                     | psp-p                  |                   |

| Deterministic officer (Notes 1, 4, 0) | Du                                      | 1244Mbps                          |                                             | -                         | 14 30                  | P9P-P             |

| LVPECL Output Low Voltage             | V <sub>OL</sub>                         | Terminated $50\Omega$ to          | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C$ | V <sub>CC</sub> - 1.81    | V <sub>CC</sub> - 1.62 | <u> </u>          |

| EVI EGE Output Eow Voltage            |                                         | V <sub>CC</sub> - 2V              | $T_A = -40^{\circ}C$ to $0^{\circ}C$        | V <sub>CC</sub> - 1.788   | V <sub>CC</sub> - 1.58 |                   |

| LVPECL Output High Voltage            | VoH                                     | Terminated $50\Omega$ to $V_0$    | V <sub>CC</sub> -<br>1.025                  | V <sub>CC</sub> -<br>0.88 | \ \/                   |                   |

| Data Output Edge Speed                |                                         | 20% to 80%<br>(Notes 1, 4, 5, 7)  | 1                                           | 50 265                    | ps                     |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}. \text{ Typical values at } V_{CC} = +3.3V, V_{IN} = 4\text{mVp-p}, \text{ and } T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted Input (IN+, IN-) terminated with } 100\Omega \text{ resistors to } V_{CC}.)$

| PARAMETER                         | SYMBOL       | CONDITIONS                | MIN                       | TYP                       | MAX                                     | UNITS             |

|-----------------------------------|--------------|---------------------------|---------------------------|---------------------------|-----------------------------------------|-------------------|

| LVPECL INPUT SPECIFICATIONS       | S (RST+, RST | -, HOLD+, HOLD-) (Note 8) |                           |                           |                                         |                   |

| LVPECL-Differential Input Voltage | VIN          |                           | 200                       |                           | 1600                                    | mV <sub>P-P</sub> |

| LVPECL Input Common-Mode<br>Range | VСМ          |                           | V <sub>CC</sub> -<br>1.49 | V <sub>CC</sub> -<br>1.32 | V <sub>CC</sub> -<br>V <sub>IN</sub> /4 | V                 |

| LVPECL Input Current              |              |                           | -150                      |                           | 190                                     | μΑ                |

- Note 1: AC parameters are guaranteed by design and characterization.

- Note 2: Supply current is measured with LVPECL data outputs open.

- **Note 3:** PSNR is measured on the differential output signal while applying a 100mV<sub>P-P</sub> sinusoidal signal at the power supply with the input open, and the DC cancellation loop activated.

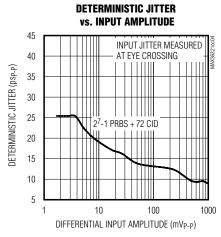

- **Note 4:** Input-data transition time controlled by 4th order bessel filter with f<sub>-3dB</sub> = 0.75 x data rate. The deterministic jitter caused by this filter is not included in the DJ specifications.

- Note 5: Measured with a repeating 0000011111 data pattern at 1244Mbps.

- **Note 6:** Deterministic jitter is measured at the differential-output eye crossing. Peak-to-peak input deterministic jitter is subtracted from peak-to-peak output deterministic jitter.

- **Note 7:** Each output (OUT+, OUT-) terminated with  $R_{LOAD} = 50\Omega$  and  $C_{LOAD} = 4pF$ .

- Note 8: The HOLD input transition time, 20% to 80%, must be less than 0.3ns for timing method 3. See Figure 10.

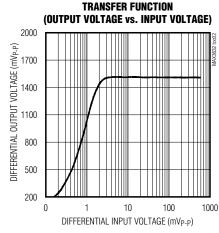

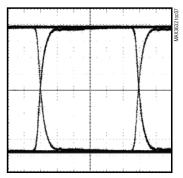

## Typical Operating Characteristics

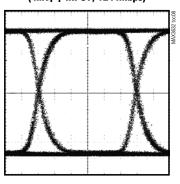

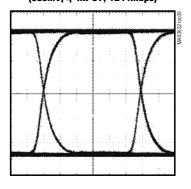

(Input signal is unfiltered,  $V_{CC} = +3.3V$ ,  $T_A = +25^{\circ}C$ , unless otherwise specified.)

### Typical Operating Characteristics (continued)

(Input signal is unfiltered,  $V_{CC} = +3.3V$ ,  $T_A = +25$ °C, unless otherwise specified.)

ELECTRICAL EYE DIAGRAM (800mV<sub>P-P</sub> INPUT, 622Mbps)

ELECTRICAL EYE DIAGRAM (4mV<sub>P-P</sub> INPUT, 1244Mbps)

ELECTRICAL EYE DIAGRAM (800mV<sub>P-P</sub> INPUT, 1244Mbps)

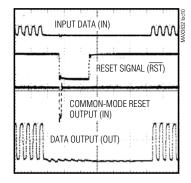

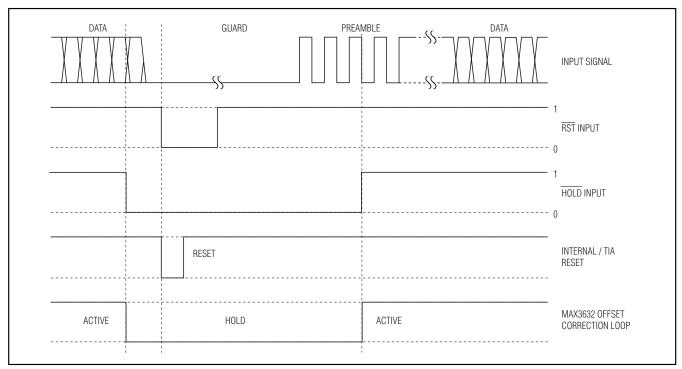

RESET TIMING DIAGRAM

### **Pin Description**

| PIN                         | NAME              | FUNCTION                                                                                                                                          |  |  |  |  |

|-----------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1, 6, 7,<br>13, 19, 24      | GND               | Ground                                                                                                                                            |  |  |  |  |

| 2, 5, 10, 14,<br>17, 20, 21 | Vcc               | +3.3V Supply Voltage                                                                                                                              |  |  |  |  |

| 3                           | IN+               | Positive Data Input, Common-Mode Reset Output                                                                                                     |  |  |  |  |

| 4                           | IN-               | Negative Data Input, Common-Mode Reset Output                                                                                                     |  |  |  |  |

| 8                           | RST+              | Positive Burst-Mode Reset Input, LVPECL Compatible                                                                                                |  |  |  |  |

| 9                           | RST-              | Negative Burst-Mode Reset Input, LVPECL Compatible                                                                                                |  |  |  |  |

| 11                          | HOLD+             | Positive Offset Correction Loop Hold Input, LVPECL Compatible                                                                                     |  |  |  |  |

| 12                          | HOLD-             | Negative Offset Correction Loop Hold Input, LVPECL Compatible                                                                                     |  |  |  |  |

| 15                          | OUT-              | Negative Data Output, LVPECL                                                                                                                      |  |  |  |  |

| 16                          | OUT+              | Positive Data Output, LVPECL                                                                                                                      |  |  |  |  |

| 18                          | N.C.              | No External Connection. Leave open.                                                                                                               |  |  |  |  |

| 22                          | CAZ2              | Offset Correction Loop Capacitor Connection. Place a 330nF capacitor between CAZ1 and CAZ2.                                                       |  |  |  |  |

| 23                          | CAZ1              | Offset Correction Loop Capacitor Connection. Place a 330nF capacitor between CAZ1 and CAZ2.                                                       |  |  |  |  |

| EP                          | Exposed<br>Paddle | Ground. Must be soldered to the circuit board ground for proper thermal and electrical performance (see <i>Exposed Pad (EP) Package</i> section). |  |  |  |  |

### Detailed Description

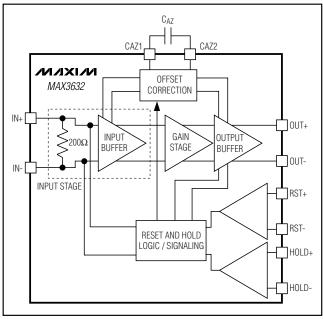

The MAX3632 burst-mode limiting amplifier is designed for 622Mbps or 1244Mbps GPON OLT receiver applications. It operates, together with the MAX3630/MAX3631 burst-mode transimpedance amplifiers, to convert current from a photodiode into an LVPECL output signal. The MAX3632 contains a data input stage, a gain stage, an offset correction loop, a reset and hold section, and an LVPECL output buffer.

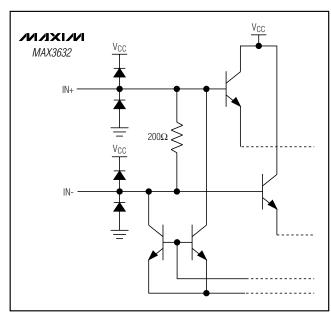

#### Input Stage

The MAX3632 input stage provides a  $200\Omega$  differential termination and buffers the data input signal. Using a proprietary common-mode signaling technique, the input stage of the MAX3632 also sends the burst-mode reset signal from the  $\overline{RST}$  inputs ( $\overline{RST}$ +,  $\overline{RST}$ -) to the MAX3630/MAX3631 TIAs. By using the common mode of the differential pair for the TIAs burst-mode reset signal, the MAX3630/MAX3631 TIAs can be assembled into 4-pin TO headers that reduce assembly costs and complexity. For proper operation of the reset signal, the MAX3630/MAX3631 data outputs (OUT+, OUT-) must be DC-coupled to the MAX3632 data inputs (IN+, IN-).

Figure 1. Functional Diagram

#### **Gain Stage/Offset Correction Loop**

The high-bandwidth gain stage of the MAX3632 provides approximately 64dB of gain. The large gain of a limiting amplifier makes it susceptible to DC offsets in the signal path that are caused by pulse-width distortion of the input signal, as well as internal offsets. The offset correction loop of the MAX3632 cancels the internal and external offsets in the signal path, which reduces the deterministic jitter at the output.

#### **Reset and Hold Section**

The offset correction loop is a necessary component for proper operation of a high-gain limiting amplifier; however, it introduces a low-frequency cutoff in the signal path. If the offset correction loop is not controlled, the low-frequency cutoff prohibits burst-mode operation. Using the RST and optional HOLD input(s), the offset correction loop can be enabled or disabled, allowing proper operation of the limiting amplifier in burst-mode applications.

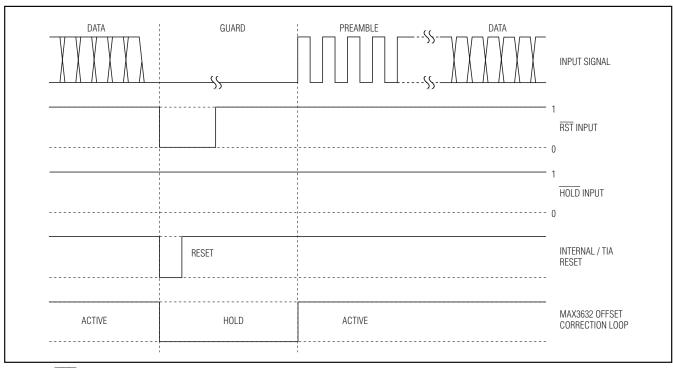

The LVPECL-compatible reset input (RST) is used to transmit a reset signal to the MAX3630/MAX3631 TIAs. When the RST input transitions low, a reset signal is generated by the internal logic and transmitted to the MAX3630/MAX3631 TIAs as described above in the *Input Stage* section. The data input (IN) must be a logic zero when RST is asserted during the guard time (Figure 7). The RST signal is also used to disable (hold) the offset correction loop until the first transition is detected by the reset and hold logic, thus indicating the beginning of the next burst signal. The hold input (HOLD) may be used to provide alternative offset cancellation control modes. Timing and operation of the RST and HOLD inputs are described in more detail in the *Applications Information* section.

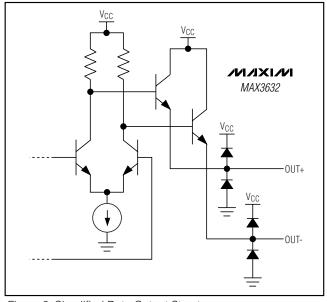

#### **LVPECL Output Buffer**

The output buffer provides a high-speed LVPECL signal. For burst-mode applications, each output (OUT+, OUT-) must be DC-coupled to an equivalent LVPECL termination.

### Design Procedure

#### **IN and OUT Terminations Requirements**

The IN+ and IN- inputs (Figure 2) of the MAX3632 must be DC-coupled to the MAX3630/MAX3631 data outputs for burst-mode operation. No external termination components are necessary between the MAX3632 and MAX3630/MAX3631 (see the *Typical Applications Circuit* section). The proper termination for each output of the MAX3632 OUT+, OUT- (Figure 3), is  $50\Omega$  to VCC - 2V. An equivalent LVPECL termination technique (e.g., Thevenin termination) may be used as long as OUT+

Figure 2. Simplified Data Input Structure

Figure 3. Simplified Data Output Structure

and OUT- are DC-coupled to the load. For more information on PECL terminations and how to interface with other logic families, refer to Maxim Application Note HFAN-01.0: *Introduction to LVDS, PECL, and CML*.

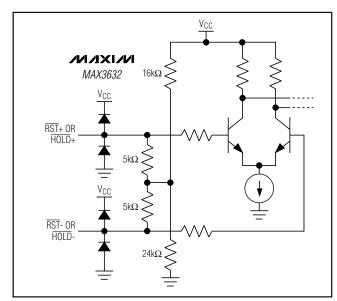

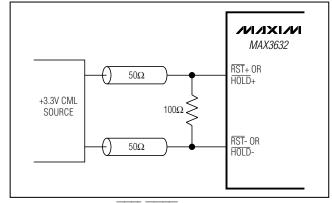

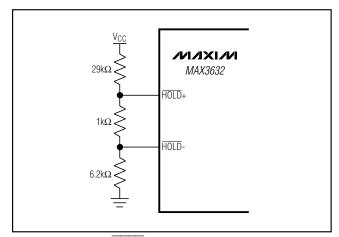

# RST and HOLD Input Termination Requirements

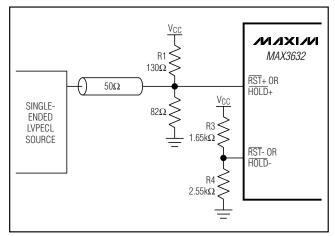

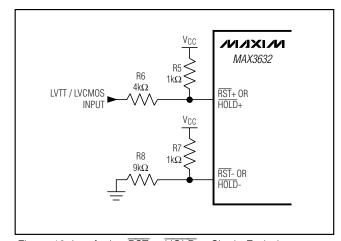

The MAX3632 RST and HOLD inputs are LVPECL compatible and internally biased (high impedance; see Figure 4). Although the inputs are compatible with LVPECL signals, it is not necessary to drive the MAX3632 RST and HOLD inputs with a standard LVPECL signal. The RST and HOLD inputs of the MAX3632 operate properly as long as the specified common-mode voltage and differential voltage swings are met.

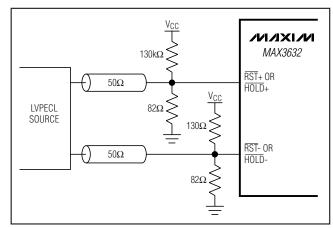

Figures 5 and 6 show how to connect an LVPECL or CML signals to the MAX3632 RST and HOLD inputs. For more information on interfacing a single-ended LVPECL or LVTTL signal to the RST or HOLD input, see *Single-Ended Operation of RST and HOLD* in the *Applications Information* section.

#### Selecting the Offset-Correction Capacitor (CAZ)

The capacitor between CAZ1 and CAZ2 determines the time constant and low-frequency cutoff (f<sub>OC</sub>) of the offset correction loop. To maintain stability, there must be a one decade separation between the data input frequency (f<sub>IN</sub>) and the low-frequency cutoff (f<sub>OC</sub>) of the offset correction loop. For GPON systems operating at 622Mbps or 1244Mbps, a 330nF capacitor (CAZ) connected between pins 22 (CAZ2) and 23 (CAZ1) is recommended. With this capacitor, the low-frequency cutoff of the offset correction loop is low enough (f<sub>OC</sub> < 30kHz) to tolerate 72 CIDs within a burst signal.

# Applications Information

#### **RST and HOLD Timing / Operation**

The RST and HOLD LVPECL-compatible inputs of the MAX3632 provide three different modes for disabling (holding) the offset correction loop during routine operations. The first mode of operation requires the single reset input, RST, which is the same signal used to create the reset signal for the MAX3630/MAX3631 TIAs to arm its threshold setting circuitry. Refer to the MAX3630/ MAX3631 data sheet and the Input Stage section for additional information. For this method, illustrated in Figure 7, the RST signal disables (holds) the offset correction loop until the transition detector in the MAX3632 identifies the beginning of the next burst. The burstmode reset signal, RST, must occur entirely within the guard time interval to prevent corrupted data. The data input (IN) must be a logic zero when RST is asserted (Figure 7). When operating in this mode, the HOLD input should be set to a valid LVPECL high (1600mV ≥  $V_{\overline{HOLD}+} - V_{\overline{HOLD}-} \ge 200 \text{mV}$ ). If the functionality of the HOLD input is not used in the application, it can be con-

Figure 4. Simplified RST and HOLD Input Structures

Figure 5. Interfacing RST/HOLD to Differential LVPECL

Figure 6. Interfacing RST/HOLD to Differential CML

Figure 7. RST Timing Method 1

Figure 8. Asserting HOLD to a Valid LVPECL High Level

nected to a valid LVPECL-high level using three external resistors as shown in Figure 8.

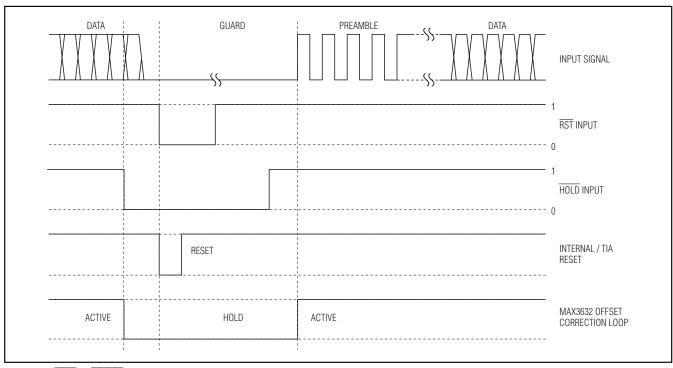

The other two optional modes of burst operation use the HOLD input. For both methods, the HOLD input should be transitioned to a low prior to the end of a burst. Using the HOLD input, the offset correction loop

is held to a known good state between the end of a data burst and the burst-mode reset signal. When the HOLD input is transitioned high again, prior to the end of the guard time, the transition detector restarts the offset cancellation loop at the beginning of the next burst (Figure 9). When the HOLD input is transitioned high again after the end of the guard time, the offset correction loop restarts (Figure 10). This mode can be used to hold a valid offset for long periods during the ranging operations.

The  $\overline{\text{RST}}$  input is edge triggered and must be transitioned low during the guard time in all cases to ensure proper operation of the MAX3630/MAX3631 burst-mode TIAs. The transition time, 20% to 80%, of the signal at the MAX3632  $\overline{\text{HOLD}}$  input, must be < 0.3ns for proper operation for method 3.

### Single-Ended Operation of RST and HOLD

The RST and HOLD inputs are designed to operate with a differential-LVPECL or -CML input signal and this is the recommended mode of operation. However, it is possible to drive the RST and HOLD inputs with a single-ended LVPECL, LVTTL, or LVCMOS signal.

Figure 9. RST or HOLD Timing Method 2

Figure 10. RST/HOLD Timing Method 3

To connect a single-ended LVPECL signal to  $\overline{RST}$  (Figure 11), connect a  $130\Omega$  resistor (R1) from  $\overline{RST}+$  or  $\overline{HOLD}+$  to  $V_{CC}$ , and an  $82\Omega$  resistor (R2) from  $\overline{RST}+$  or  $\overline{HOLD}+$  to ground. The  $\overline{RST}+$  or  $\overline{HOLD}+$  pin must also be DC-coupled to the single-ended LVPECL source. Connect a resistor (R3) from  $V_{CC}$  to  $\overline{RST}-$  or  $\overline{HOLD}-$  and another resistor (R4) from  $\overline{RST}-$  or  $\overline{HOLD}-$  to ground. The parallel combination of R3 and R4 should be less than 1k $\Omega$ . Choose the values of R3 and R4 to set the common-mode voltage in the range defined in the Electrical Characteristics table. This configuration with typical values is shown in Figure 11.

An LVTTL or LVCMOS signal may also be used if the transition time is fast enough. For single-ended operation with an LVTTL or LVCMOS signal (Figure 12), connect a 4k $\Omega$  resistor (R6) from the  $\overline{RST}+$  or HOLD+ to the signal source, and a 1k $\Omega$  resistor (R5) from  $\overline{RST}+$  or HOLD+ to VCC. A 1k $\Omega$  resistor (R7) to VCC, and a 9k $\Omega$  resistor (R8) to ground, should then be connected to  $\overline{RST}-$  or HOLD-. For typical LVTTL or LVCMOS specifications of VCC to 2.8V for a high, and 0.4V to 0V for a low, the LVTTL or LVCMOS needs to source approximately zero current and sink a maximum of approximately 720µA using this configuration.

#### **Layout Considerations**

Use good high-frequency layout techniques and multiple-layer boards with uninterrupted ground planes to minimize EMI and crosstalk. If the electrical length between the MAX3630/MAX3631 output and the MAX3632 input path delay is long compared to the input transition time, a controlled 200 $\Omega$  differential-impedance transmission line should be used to interface the two devices. A controlled-impedance transmission line of 50 $\Omega$  single-ended (100 $\Omega$  differential) should be used to interface the MAX3632 output (OUT+, OUT-) to other devices. The RST and HOLD inputs should also be connected to the LVPECL- or CML-signal source with a controlled impedance (50 $\Omega$  single ended, 100 $\Omega$  differential) transmission line. Place the CAZ capacitor as close as possible to pin 22 (CAZ2) and pin 23 (CAZ1).

#### Exposed Pad (EP) Package

The exposed-pad on the 24-pin QFN provides a very low thermal resistance path for heat removal from the IC. The pad is also electrical ground on the MAX3632 and must be soldered to the circuit board ground for proper thermal and electrical performance. Refer to Maxim Application Note HFAN-08.1: *Thermal Considerations for QFN and Other Exposed Pad Packages* (available at www.maxim-ic.com).

Figure 11. Interfacing RST or HOLD to Single-Ended LVPECL

Figure 12. Interfacing RST or HOLD to Single-Ended LVTTL/LVCMOS

## Pin Configuration

### \_Chip Information

TRANSISTOR COUNT: 1363 (1232 bipolar, 131 MOS) PROCESS: SiGe BiCMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

|       |                   |         |      | СПИІ     | NDN     | DIME   | IZNZ      | □NS     |      |           |         |      |           |      |      |

|-------|-------------------|---------|------|----------|---------|--------|-----------|---------|------|-----------|---------|------|-----------|------|------|

| PKG   | 3 12L 4×4 16L 4×4 |         |      | 4        | 20L 4×4 |        |           | 24L 4×4 |      |           | 28L 4×4 |      |           |      |      |

| REF.  | MIN.              | NDM.    | MAX. | MIN.     | NDM.    | MAX.   | MIN.      | NDM.    | MAX. | MIN.      | NDM.    | MAX. | MIN.      | NDM. | MAX. |

| Α     | 0.70              | 0.75    | 0.80 | 0.70     | 0.75    | 0.80   | 0.70      | 0.75    | 0.80 | 0.70      | 0.75    | 0.80 | 0.70      | 0.75 | 0.80 |

| A1    | 0.0               | 0.02    | 0.05 | 0.0      | 20,0    | 0.05   | 0.0       | 0.02    | 0.05 | 0,0       | 0.02    | 0.05 | 0.0       | 20.0 | 0.05 |

| A2    | 0.20 REF 0.20 REF |         |      | 0.20 REF |         |        | 0.20 REF  |         |      | 0.20 REF  |         |      |           |      |      |

| lo    | 0.25              | 0.30    | 0.35 | 0.25     | 0.30    | 0.35   | 0.20      | 0.25    | 0.30 | 0.18      | 0.23    | 0.30 | 0.15      | 0.20 | 0.25 |

| D     | 3,90              | 4.00    | 4,10 | 3.90     | 4.00    | 4.10   | 3.90      | 4.00    | 4.10 | 3.90      | 4.00    | 4.10 | 3.90      | 4.00 | 4.10 |

| Ε     | 3.90              | 4.00    | 4.10 | 3.90     | 4.00    | 4.10   | 3.90      | 4.00    | 4.10 | 3.90      | 4.00    | 4.10 | 3.90      | 4.00 | 4.10 |

| e     |                   | D.80 BS | C.   | 0        | .65 BS  | C.     | 0.50 BSC. |         |      | 0.50 BSC. |         |      | 0.40 BSC. |      |      |

| k     | 0.25              | -       | -    | 0.25     | -       | -      | 0.25      | -       | -    | 0.25      | -       | -    | 0.25      | -    | -    |

| ١     | 0.45              | 0.55    | 0.65 | 0.45     | 0.55    | 0.65   | 0.45      | 0.55    | 0.65 | 0.30      | 0.40    | 0.50 | 0.30      | 0.40 | 0.50 |

| N     |                   | 12      |      |          | 16      |        | 20        |         | 24   |           | 28      |      |           |      |      |

| ND    |                   | 3       |      | 4        |         | 5      |           | 6       |      | 7         |         |      |           |      |      |

| NE    |                   | 3       |      | 4        |         | 5      |           | 6       |      |           | 7       |      |           |      |      |

| Jedec |                   | WGGB    |      | VGGC     |         | VGGD-1 |           | WGGD-2  |      |           | VGGE    |      |           |      |      |

| EXPOSED PAD VARIATIONS |      |      |      |      |               |      |         |  |  |

|------------------------|------|------|------|------|---------------|------|---------|--|--|

| PKG.                   |      | D2   |      |      | DOWN<br>BONDS |      |         |  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM.          | MAX. | ALLOVED |  |  |

| T1244-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10          | 2.25 | YES     |  |  |

| T1244-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10          | 2.25 | ND      |  |  |

| T1644-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10          | 2.25 | YES     |  |  |

| T1644-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10          | 2.25 | ND      |  |  |

| T2044-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10          | 2.25 | YES     |  |  |

| T2044-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10          | 2.25 | ND      |  |  |

| T2444-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10          | 2.25 | YES     |  |  |

| T2444-3                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60          | 2.63 | YES     |  |  |

| T2444-4                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60          | 2.63 | ND      |  |  |

| T2844-1                | 2.50 | 2.60 | 2.70 | 2.50 | 2.60          | 2.70 | ND      |  |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- ↑ THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN

THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- (£) DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- AND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. COPLANARITY SHALL NOT EXCEED 0.08mm

- . WARPAGE SHALL NOT EXCEEND 0.10mm

-DRAWING NOT TO SCALE-

- A LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "6", ±0.05.

- 14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY

DALLAS /// IXI//

TITLE PACKAGE OUTLINE,

12, 16, 20, 24, 28L THIN QFN, 4x4x0.8mm

APPROVAL DOCUMENT DOUTREL NO. REV

21-0139

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.