# 70+70W STEREO PASTILLI POWER AMPLIFIER

- MONOCHIP BRIDGE STEREO AMPLIFIER FOR BASH® ARCHITECTURE

- 55+55W OUTPUT POWER @  $R_L = 4/8 \Omega$ , THD = 0.5%

- 70+70W OUTPUT POWER @  $R_L = 4/8 \Omega$ , THD = 10%

- HIGH DYNAMIC PREAMPLIFIER INPUT STAGES

- EXTERNAL PROGRAMMABLE FEEDBACK TYPE COMPRESSORS

- AC COUPLED INPUT TO CLASS AB BRIDGE OUTPUT AMPLIFIER

- PRECISION RECTIFIERS TO DRIVE THE DIGITAL CONVERTER

- ON-OFF SEQUENCE/ TIMER WITH MUTE AND STANDBY

- PROPORTIONAL OVER POWER OUTPUT CURRENT TO LIMIT THE DIGITAL CONVERTER

- ABSOLUTE POWER BRIDGE OUTPUT

TRANSISTOR POWER PROTECTION

- ABSOLUTE OUTPUT CURRENT LIMIT

- INTEGRATED THERMAL PROTECTION

- POWER SUPPLY OVER VOLT/\GE PROTECTION

- FLEXIWATT POWER PACKAGE WITH 27 PIN

- BASH® LICENCE REQUIRED

### DESCRIPTION'

The STASSO is a fully integrated power module designed to implement a BASH® amplifier when used in conjunction with STABP01 digital processor.

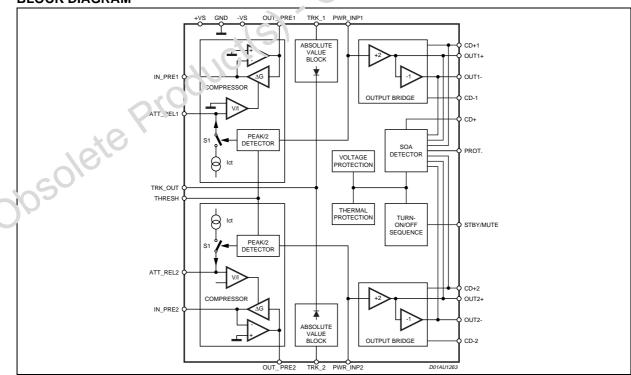

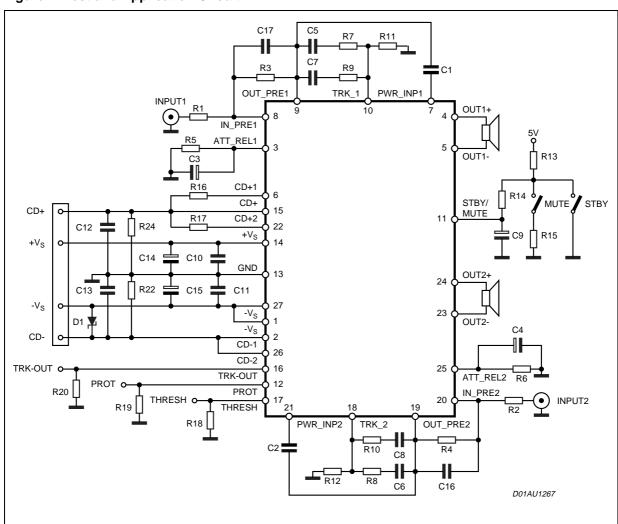

## **BLOCK DIAGRAM**

July 2003 1/16

## **DESCRIPTION** (continued)

Notice that normally only one Digital Converter is needed to supply a stereo or multi-channel amplifier system, therefore most of the functions implemented in the circuit have summing outputs

The signal circuits are biased by fixed negative and positive voltages referred to Ground. Instead the final stages of the output amplifiers are supplied by two external voltages that are following the audio signal. In this way the headroom for the output transistors is kept at minimum level to obtain a high efficiency power amplifier.

The Compressor circuits, one for each channel, performs a particular transfer behavior to avoid the dynamic restriction that an adaptive system like this requires. To have a high flexibility the attack / release time and the threshold levels are externally programmable. The tracking signal for the external digital converter is generated from the Absolute Value block that rectifies the audio signal present at the compressor output. The outputs of these blocks are decoupled by a diode to permit an easy sum of this signal for the multichannel application. The output power bridges have a dedicated input pin to perform an AC decoupling to cancel the compressor output DC offset. The gain of the stage is equal to 4 (+12dB). A sophisticated circuit performs the output transistor power detector that , with the digital converter, reduces the power supply voltage . Moreover, a maximum current output limiting and the over temperature sensor have been added to protect the circuit itself. The external voltage applied to the STBY/MUTE pin forces the two amplifiers in the proper condition to guarantee a silent turnon and turn-off.

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                         | Parameter                                                                      | Value        | Unit |

|------------------------------------------------|--------------------------------------------------------------------------------|--------------|------|

| +V <sub>s</sub>                                | Positive supply voltage referred to pin 13 (GND)                               | 30           | V    |

| -V <sub>s</sub>                                | Negative supply voltage referred to pin 13 (GND)                               | -24          | V    |

| V <sub>CD+</sub>                               | Positive supply voltage tracking rail referred to pin 13 (GND)                 | 22           | V    |

| V <sub>CD+</sub>                               | Positive supply voltage operated to Vs+ <sup>(1)</sup>                         | 0.3          | V    |

| V <sub>CD</sub> -                              | Negative supply voltage referred to -Vs <sup>(1)</sup>                         | -0.3         | V    |

| V <sub>CD</sub> -                              | Negative supply voltage tracking rail referred to pin 13 (GND)                 | -22          | V    |

| V <sub>Att_Rel1</sub><br>V <sub>Att_Rel2</sub> | Pin 3, 25 Negative & Positive maximum voltage referred to GND (pin 13)         | -0.5 to +20  | V    |

| VPwr_Imp1<br>VPwr_Imp2<br>VTrk_1<br>VTrk_2     | Pin 7, 21, 18, 10 Negative & Positive maximum voltage referred to GND (pin 13) | -20 to +20   | V    |

| V <sub>In_pre1</sub><br>V <sub>In_pre2</sub>   | Pin 8, 20 Negative & Positive maximum voltage referred to GND (pin 13)         | -0.5 to +0.5 | V    |

| V <sub>threshold</sub>                         | Pin 17 Negative & Positive maximum voltage referred to GND (pin 13)            | -7 to +0.5   | V    |

| I <sub>stb-max</sub>                           | Pin 11 maximum input current (Internal voltage clamp at 5V)                    | 500          | μΑ   |

| V <sub>stbymute</sub>                          | Pin 11 negative maximum vol <sub>t</sub> age referred to GND (pin 13)          | -0.5         | V    |

| lout                                           | Output Current                                                                 | 7.0          | Α    |

Note 1:  $V_{CD-}$  must not be more negative than -Vs and  $V_{CD+}$  must not be more positive than +Vs

Note 2: All pins withstand ±2KV ESD but not pin 11

**477**

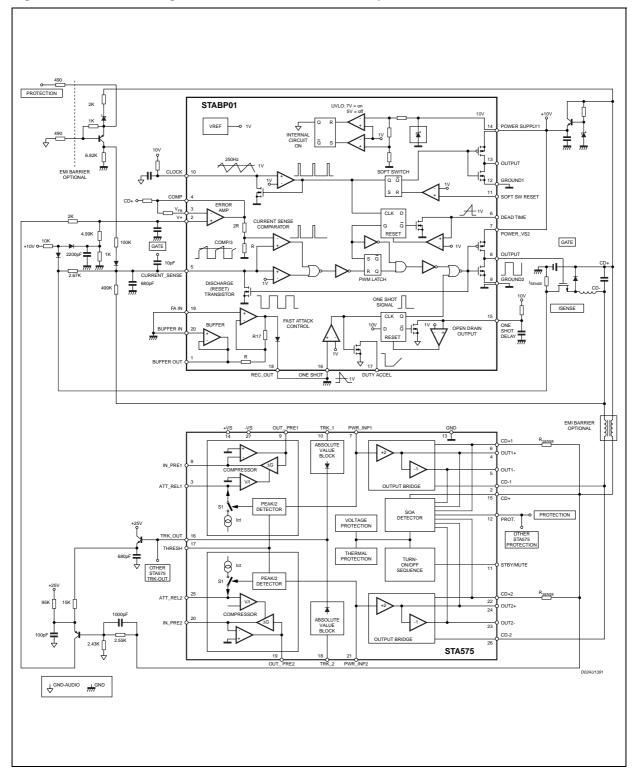

Figure 1. Connection Diagram between STA550 and STAbp01

# THERMAL DATA

| Symbol                 | Parameter                               | Value | Unit |

|------------------------|-----------------------------------------|-------|------|

| Tj                     | Max Junction temperature                | 150   | °C   |

| R <sub>th j_case</sub> | Thermal Resistance Junction to case max | 1     | °C/W |

# **OPERATING RANGE**

| Symbol                 | Parameter                                                        | Value                   | Unit    |

|------------------------|------------------------------------------------------------------|-------------------------|---------|

| +V <sub>s</sub>        | Positive supply voltage                                          | +20 to +30              | V       |

| -V <sub>s</sub>        | Negative supply voltage                                          | -10 to -22              | V       |

| ΔV <sub>S+</sub>       | Delta positive supply voltage                                    | 5V ≤ (Vs+ - VCD+) ≤ 10V | V       |

| V <sub>CD+</sub>       | Positive supply voltage tracking rail                            | +3 to 17                | V       |

| V <sub>CD</sub> -      | Negative supply voltage tracking rail                            | -17 to -3               | V       |

| I <sub>in_Max</sub>    | Current at pin In_Pre1, In_Pre2, related to compressor behaviour | -1 to +1                | mA peak |

| V <sub>trheshold</sub> | Voltage at pin Threshold                                         | -5 to 0                 | V       |

| T <sub>amb</sub>       | Ambient Temperature Range                                        | 0 to 70                 | °C      |

| I <sub>sb_max</sub>    | Pin 11 maximum input current (Internal voltage clmp at 5V)       | 200                     | μΑ      |

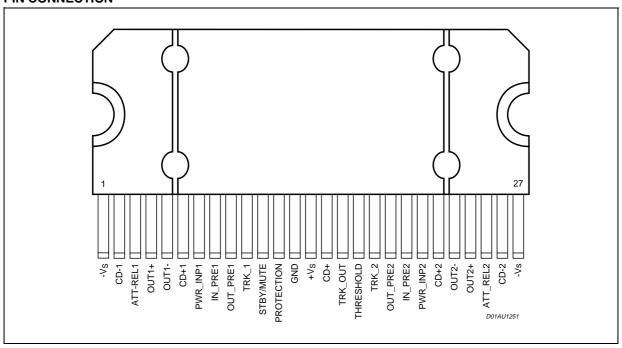

# **PIN CONNECTION**

# **PIN FUNCTION**

| N° | Name       | Description                                                |  |  |  |

|----|------------|------------------------------------------------------------|--|--|--|

| 1  | -Vs        | Negative Bias Supply                                       |  |  |  |

| 2  | CD-1       | Channel 1 Time varying tracking rail negative power supply |  |  |  |

| 3  | Att_Rel1   | ttack release rate for channel 1                           |  |  |  |

| 4  | Out1+      | Channel 1 speaker positive output                          |  |  |  |

| 5  | Out1-      | Channel 1 speaker negative output                          |  |  |  |

| 6  | CD+1       | Channel 1 positive power supply                            |  |  |  |

| 7  | Pwr_Inp1   | Input to channel 1 power stage                             |  |  |  |

| 8  | In_pre1    | Pre-amp input for channel 1 (virtual ground)               |  |  |  |

| 9  | Out_pre1   | Output channel 1 pre-amp                                   |  |  |  |

| 10 | Trk_1      | Absolute value block input for channel 1                   |  |  |  |

| 11 | Stby/mute  | Standby/mute input voltage control                         |  |  |  |

| 12 | Protection | Protection signal for STABP01 digital processor            |  |  |  |

| 13 | Gnd        | Analog Ground                                              |  |  |  |

| 14 | +Vs        | Positive Bias Supply                                       |  |  |  |

| 15 | CD+        | Time varying tracking rail positive power supply           |  |  |  |

| 16 | Trk_out    | Reference output for STABP01 digital processor             |  |  |  |

| 17 | Threshold  | Compressor threshold input                                 |  |  |  |

| 18 | Trk_2      | Absolute value block input for channel 2                   |  |  |  |

| 19 | Out_pre2   | Output channel 2 pre-amp                                   |  |  |  |

| 20 | In_pre2    | Pre-amp input for channel 2 (virtual ground)               |  |  |  |

| 21 | Pwr_Inp2   | Input to channel 2 power stage                             |  |  |  |

| 22 | CD+2       | Channel 2 positive power supply                            |  |  |  |

| 23 | Out2-      | Channel 2 speaker negative output                          |  |  |  |

| 24 | Out2+      | Channel 2 speaker positive output                          |  |  |  |

| 25 | Att_Rel2   | Attack release rate for channel 2                          |  |  |  |

| 26 | CD-2       | Channel 2 Time varying tracking rail negative power supply |  |  |  |

| 27 | -Vs        | Negative Bias Supply                                       |  |  |  |

**ELECTRICAL CHARACTERISTCS** (Test Condition: Vs+=26V, Vs-=-22V,  $V_{CD+}=17V$ ,  $V_{CD-}=-17V$ ,  $R_L=8\Omega$ , external components at the nominal value f=1KHz,  $Tamb=25^{\circ}C$  unless otherwise specified

| Symbol                    | Parameter                                    | Test Condition                                                                                                                      | Min.                | Тур.                          | Max.             | Unit           |

|---------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|------------------|----------------|

| PREAMPL                   | IFIER AND COMPRESSOR                         |                                                                                                                                     |                     | I                             |                  | I              |

| V <sub>out clamp</sub>    | Maximum Voltage at Out_pre pin               |                                                                                                                                     | 10                  | 11                            | 12               | Vpeak          |

| l <sub>in</sub>           | Audio input current                          |                                                                                                                                     |                     |                               | 0.8              | mA             |

| V <sub>control</sub>      | Voltage at Attack_Release pin                | Attenuation = 0dB<br>Attenuation = 6dB<br>Attenuation = 26dB                                                                        | 0.35<br>6           | 0<br>0.5<br>9                 | 0.65<br>12       | V<br>V<br>V    |

| VC <sub>omp</sub> _<br>Th | Input voltage range for the compression      |                                                                                                                                     | -5                  |                               | -1               | V              |

| $Z_{th}$                  | Input impedance of Threshold pin             |                                                                                                                                     | 100                 |                               |                  | ΚΩ             |

| Voffset                   | Output Offset at Out_pre pin with:           | V <sub>CRT</sub> = 0V; Attenuation = 0dB<br>V <sub>CRT</sub> = 0.5V; Attenuation = 6dB<br>V <sub>CRT</sub> = 9V; Attenuation = 26dB | -10<br>-250<br>-450 |                               | 10<br>250<br>450 | mV<br>mV<br>mV |

| THD                       | Distortion at Out_pre:                       | V <sub>CRT</sub> = 0V; Attenuation = 0dB<br>V <sub>CRT</sub> = 0.5V; Attenuation = 6dB<br>V <sub>CRT</sub> = 9V; Attenuation = 26dB |                     | 0.01                          | 5<br>5           | %<br>%<br>%    |

| EN                        | Noise at Out_pre pin :                       | V <sub>CRT</sub> = 0V; Attenuation = 0dB<br>V <sub>CRT</sub> = 0.5V; Attenuation = 6dB<br>V <sub>CRT</sub> = 9V; Attenuation = 26dB |                     | 10 <sup>(2)</sup><br>50<br>60 |                  | μV<br>μV<br>μV |

| I <sub>ct</sub>           | Attack time current at pin<br>Attack_release |                                                                                                                                     |                     | 1.5                           |                  | mA             |

<sup>1.</sup> This value is due to the thermal noise of the external resistors  $R_r$  and  $R_i$ .

| TRACKIN              | G PARAMETERS                                   |                                                                                                                   |          |          |     |        |

|----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------|----------|-----|--------|

| G <sub>trk</sub>     | Tracking reference voltage gain                |                                                                                                                   | 13       | 14       | 15  | V      |

| V <sub>trk_out</sub> | Tracking ref. output voltage                   |                                                                                                                   | 0        | 20       |     | V      |

| I <sub>trk_out</sub> | Current capability                             |                                                                                                                   | 5        | 6        | 7   | mA     |

| Z <sub>trk_in</sub>  | Input impedance (T <sub>RK1/2</sub> )          |                                                                                                                   |          | 1        |     | MΩ     |

| OUTPUT               | BRIDGE                                         |                                                                                                                   | ı        | •        | •   |        |

| G <sub>out</sub>     | Half Output bridge gain                        |                                                                                                                   | 5.5      | 6        | 6.5 | dB     |

| G <sub>ch</sub>      | Output bridge differential gain                |                                                                                                                   | 11       | 12       | 13  | dB     |

| $\Delta G_ch$        | Output bridges gain mismatch                   |                                                                                                                   | -1       |          | 1   | dB     |

| P <sub>out</sub>     | Continuous Output Power                        | THD = 0.5%<br>THD = 10%                                                                                           | 50<br>64 | 55<br>70 |     | W<br>W |

|                      |                                                | THD = 10%; $R_L$ = 4 $\Omega$ ; $V_{CD+}$ = 13 $V$ ; $V_{CD-}$ = -13 $V$ ; $V_{S+}$ = 20 $V$ ; $V_{S-}$ = -20 $V$ | 64       | 70       |     | W      |

| THD                  | Total harmonic distortion of the output bridge | Po = 5W                                                                                                           |          | 0.01     |     | %      |

|                      | output bridge                                  | f = 20Hz to 20KHz; Po = 30W                                                                                       |          |          | 0.1 | %      |

| V <sub>Off</sub>     | Output bridge D.C. offset                      |                                                                                                                   |          |          | 50  | mV     |

# **ELECTRICAL CHARACTERISTCS** (continued)

| Symbol              | Parameter                                         | Test Condition                                                                               | Min. | Тур.              | Max. | Unit           |

|---------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------|------|-------------------|------|----------------|

| EN                  | Noise at Output bridge pins                       | $f = 20Hz$ to $20KHz$ ; $Rg = 50\Omega$                                                      |      | 12                |      | μV             |

| Z <sub>br_in</sub>  | Input impedance                                   |                                                                                              | 100  | 140               | 180  | ΚΩ             |

| R <sub>dson</sub>   | Output power Rdson                                | I <sub>O</sub> = 1A                                                                          |      | 200               | 400  | mΩ             |

| OLG                 | Open Loop Voltage Gain                            |                                                                                              |      | 100               |      | dB             |

| GB                  | Unity Gain Bandwidth                              |                                                                                              |      | 1.4               |      | MHz            |

| SR                  | Slew Rate                                         |                                                                                              |      | 7                 |      | V/µs           |

| PROTECT             | TON                                               |                                                                                              |      | •                 | •    |                |

| V <sub>stby</sub>   | Stby voltage range                                |                                                                                              | 0    |                   | 0.8  | V              |

| V <sub>mute</sub>   | Mute voltage range                                |                                                                                              | 1.6  |                   | 3    | V              |

| $V_{play}$          | Play voltage range                                |                                                                                              | 4    |                   | 5    | V              |

| T <sub>h1</sub>     | First Over temperature threshold                  |                                                                                              |      | 130               |      | °C             |

| T <sub>h2</sub>     | Second Over temperature threshold                 |                                                                                              |      | 150               |      | °C             |

| Unbal.<br>Ground    | Upper Unbalancing ground threshold                | Referred to (CD <sup>+</sup> - CD <sup>-</sup> )/2                                           |      | 5                 |      | V              |

| Unbal.<br>Ground    | Lower Unbalancing ground threshold                | Referred to (CD <sup>+</sup> - CD <sup>-</sup> )/2                                           |      | -5                |      | V              |

| UV <sub>th</sub>    | Under voltage threshold                           | Vs+  +  Vs-                                                                                  |      | 20                |      | V              |

| P <sub>d_reg.</sub> | Power dissipation threshold for system regulation | $I_{prot} = 50 \mu A$ ; @ Vds = 10V                                                          | 25   |                   | 31   | W              |

| P <sub>d_max</sub>  | Switch off power dissipation threshold            | @ Vds = 10V                                                                                  |      | 48                |      | W              |

| I <sub>prot</sub>   | Protection current slope                          | for Pd > Pd <sub>reg</sub>                                                                   |      | 400               |      | μA/W           |

| I <sub>Ict</sub>    | Limiting Current threshold                        |                                                                                              | 5.5  | 6                 | 6.5  | А              |

| I+Vs                | Positive supply current                           | Stby (Vstby/mute pin = 0V) Mute (Vstby/mute pin = 2.5V) Play (Vstby/mute pin = 5V no signal) |      | 4<br>35<br>35     |      | mA<br>mA<br>mA |

| I-Vs                | Negative supply current                           | Stby (Vstby/mute pin = 0V) Mute (Vstby/mute pin = 2.5V) Play (Vstby/mute pin = 5V no signal) |      | 4<br>35<br>35     |      | mA<br>mA<br>mA |

| ICD+                | Positive traking rail supply current              | Stby (Vstby/mute pin = 0V) Mute (Vstby/mute pin = 2.5V) Play (Vstby/mute pin = 5V no signal) |      | 100<br>110<br>110 |      | μΑ<br>mA<br>mA |

| ICD-                | Negative traking rail supply current              | Stby (Vstby/mute pin = 0V) Mute (Vstby/mute pin = 2.5V) Play (Vstby/mute pin = 5V no signal) |      | 100<br>110<br>110 |      | μΑ<br>mA<br>mA |

### **FUNCTIONAL DESCRIPTION**

The circuit contains all the blocks to build a stereo amplifier. Each single channel is based on the Output Bridge Power Amplifier, and its protection circuit. Moreover, the compression function and a signal rectifier are added to complete the circuit.

The operation modes are driven by The Turn-on/off sequence block. In fact the IC can be set in three states by the Stby/mute pin:

Standby ( $V_{pin} < 0.8V$ ), Mute (1.6V <  $V_{pin} < 3V$ ), and Play ( $V_{pin} > 4V$ ).

In the Standby mode all the circuits involved in the signal path are in off condition, instead

in Mute mode the circuits are biased but the Speakers Outputs are forced to ground potential.

These voltages can be get by the external RC network connected to Stby/Mute pin.

The same block is used to force quickly the I.C. In standby mode or in mute mode when the I.C. dangerous condition has been detected. The RC network in these cases is used to delay the Normal operation restore.

The protection of the I.C. are implemented by the Over Temperature, Unbalance Ground, Output Short circuit, Under voltage, and output transistor Power sensing as shown in the following table:

**Table 1. Protection Implementation**

| Fault Type                                     | Condition                         | Protection strategy                        | Action time                      | Release time                         |

|------------------------------------------------|-----------------------------------|--------------------------------------------|----------------------------------|--------------------------------------|

| Chip Over temperature                          | Tj > 130 °C                       | Mute                                       | Fast                             | Slow Related to Turn_on sequence     |

| Chip Over temperature                          | Tj > 150 °C                       | Standby                                    | Fast                             | Slow, Related to<br>Turn_on sequence |

| Unbalancing<br>Ground                          | Vgnd  > ((CD+) -<br>(CD-))/2 + 5V | Standby                                    | Fast                             | Slow, Related to Turn_on sequence    |

| Short circuit                                  | lout > 6A                         | Standby                                    | Fast                             | Slow, related to Turn_on sequence    |

| Under Voltage                                  | Vs+  +  Vs- < 20V                 | Standby                                    | Fast                             | Slow, related to Turn_on sequence    |

| Extra power dissipation at output transistor   | Pd tr. >25W                       | Reducing DIGITAL CONVERTER output voltage. | Related to the DIGITAL CONVERTER | Related to the DIGITAL CONVERTER     |

| Maximum power dissipation at output transistor | Pd tr. > 48W                      | Standby                                    | Fast                             | Slow, related to<br>Turn_on sequence |

See the POWER PROTECTION paragraph for the details

## Compression

An other important function implemented, to avoid high power dissipation and clipping distortion, is the Compression of the signal input. In fact the preamplifier stage performs a voltage gain equal to 5, fixed by Ri and Rr external resistor, but in case of high input signal or low power supply voltage, its gain could be reduced of 26dB. This function is obtained with a feedback type compressor that , in practice, reduces the impedance of the external feedback network. The behavior of compression it's internally fixed but depends from the Audio input voltage signal level, and from the Threshold voltage applied to the Threshold pin. The attack and release time are programmable by the external RC network connected to the Att\_Rel pins.

The constraints of the circuit in the typical application are the following:

Vthreshold range = -5 to 0

Vin peak max = 8V

Vout peak max = 10V

Gain without compression (G) = 5 Max Attenuation ratio = 26 dB

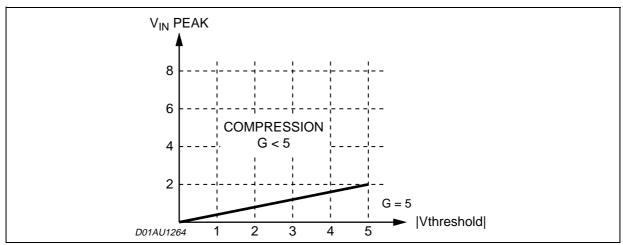

The following graph gives the representation of the Compressor activation status related to the Vthreshold and the input voltage. The delimitation line between the two fields, compression or not, is expressed by the formula:

$$V_{in} = \frac{2 \cdot |Vthreshold|}{G}$$

Where G is the preamplifier gain without compression.

In the compression region the gain of the preamplifier will be reduced

$(G = 2 \cdot Vthreshold/Vin)$  to maintain at steady state the output voltage equal 2\*|Vthreshold|.

Instead in the other region the compressor will be off (G = 5).

The delimitation line between the two fields can be related to the output voltage of the preamplifier: in this case the formula is:

$$V_{out} = 2 \cdot |Vthreshold|$$

Figure 2. Compressor activation field

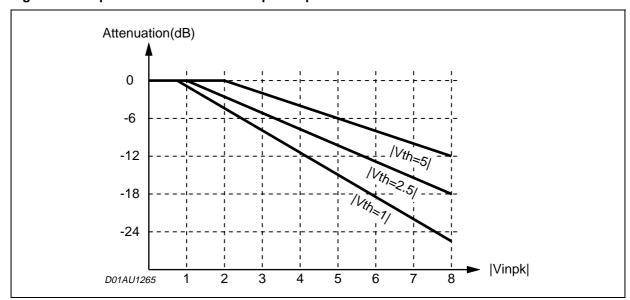

The relative attenuation introduced by the variable gain cell is the following:

$$Attenuation = 20log \frac{2}{5} \cdot \frac{\left|V_{th}\right|}{V_{in\_peak}}$$

The total gain of the stage will be:

The maximum input swing is related to the value of input resistor, to guarantee that the input current remain under lin\_Max value (1 mA).

$$R_i > \frac{V_{in\_peak}}{I_{in\_max}}$$

Figure 3. Compressor attenuation vs. input amplitude

### **ABSOLUTE VALUE BLOCK**

The absolute value block rectifies the signal after the compression to extract the control voltage for the external digital converter. The output voltage swing is internally limited, the gain is internally fixed to 14.

The input impedance of the rectifier is very high, to allow the appropriate filtering of the audio signal before the rectification (between Out pre and Trk pins).

## **OUTPUT BRIDGE**

The Output bridge amplifier makes the single-ended to Differential conversion of the Audio signal using two power amplifiers, one in non-inverting configuration with gain equal to 2 and the other in inverting configuration with unity gain. To guarantee the high input impedance at the input pins, Pwr\_Inp1 and Pwr\_Inp2, the second amplifier stages are driven by the output of the first stages respectively.

## **POWER PROTECTION**

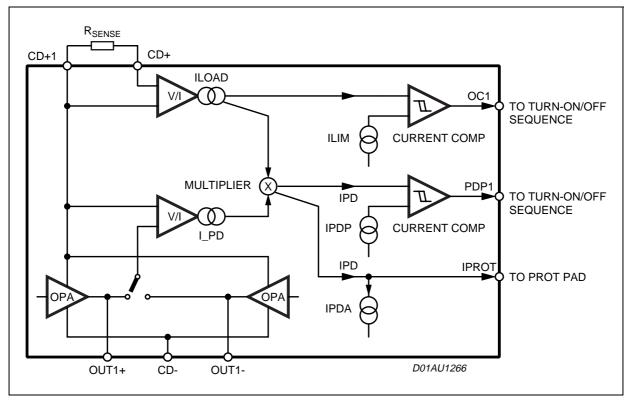

To protect the output transistors of the power bridge a power detector is implemented (fig 3).

The current flowing in the power bridge and trough the series resistor Rsense is measured reading the voltage drop between CD+1 and CD+. In the same time the voltage drop on the relevant power (Vds) is internally measured. These two voltages are converted in current and multiplied: the resulting current , lpd, is proportional to the instantaneous dissipated power on the relevant output transistor. The current lpd is compared with the reference current lpda, if bigger (dissipated power > 25W) a current, lprot, is supplied to the Protection pin. The aim of the current lprot is to reduce the reference voltage for the digital converter supplying the power stage of the chip, and than to reduce the dissipated power. The response time of the system must be less than  $200\mu$ Sec to have an effective protection. As further protection, when lpd reaches an higher threshold (when the dissipated value is higher then 48W) the chip is shut down, forcing low the Stby/Mute pin, and the turn on sequence is restarted.

Figure 4. Power Protection Block Diagram

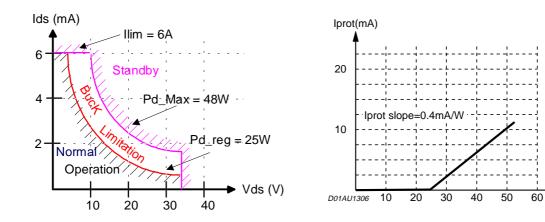

In fig. 4 there is the power protection strategy pictures. Under the curve of the 25W power, the chip is in normal operation, over 48W the chip is forced in Standby. This last status would be reached if the digital converter does not respond quikly enough reducing the stress to less than 48W.

The fig.5 gives the protection current, Iprot, behavior. The current sourced by the pin Prot follows the formula:

$$I_{prot} \equiv \frac{(P_d - P_{d_av_th}) \cdot 5 \cdot 10^{-4}}{1.25 \text{ V}}$$

for  $P_d < P_{d\_av\_th}$  the  $I_{prot} = 0$

Independently of the output voltage, the chip is also shut down in the following conditions:

When the currentthrough the sensing resistor, R<sub>sense</sub>, reaches 6A (Voltage drop (CD+) - (CD+1) = 700mV).

When the average junction temperature of the chip reaches 150°C.

When the ground potential differ from more than 5V from the half of the power supply voltage, ((CD+)-(CD-))/2 When the sum of the supply voltage |Vs+| + |Vs-| < 20V

The output bridge is muted when the average junction temperature reaches 130°C.

Figure 5. Power protection threshold

Figure 6. Protection current behaviour

Pd(W)

Figure 7. Test and Application Circuit

# **EXTERNAL COMPONENTS**

| Name           | Function                                    | Value                                                         | Formula                                   |

|----------------|---------------------------------------------|---------------------------------------------------------------|-------------------------------------------|

| Ri<br>R1 = R2  | Input resistor                              | $10K\Omega$ ( G  = 5, Rr = 50K\O)                             | $R_i = \frac{Rr}{ G }$                    |

| Rr<br>R3 = R4  | Feedback resistor                           | 50KΩ<br>( G  = 5, Ri = 10KΩ                                   | $Rr =  G  \cdot Rr$                       |

| Cac<br>C1 = C2 | AC Decoupling capacitor                     | 100nF<br>(fp = 16Hz,<br>Rac =100KΩ )                          | $Cac = \frac{1}{2\pi \cdot fp \cdot Rac}$ |

| Cct<br>C3 = C4 | Capacitor for the attack time               | 2.2μF<br>(Tattack = 13mSec,<br>Vcontrol = 9V,<br>Ict = 1.5mA) | $Cct = attack \frac{Ict}{Vcontrol}$       |

| R5 = R6        | Release constant time Resistor              | 470KΩ (t = 1 Sec. , Cct = 2.2 μF )                            | $Rct = \frac{\tau}{Cct}$                  |

| R7 = R8        | Resistor for tracking input voltage filter  | 10ΚΩ                                                          |                                           |

| R9 = R10       | Resistor for tracking input voltage filter  | 56ΚΩ                                                          |                                           |

| R11 = R12      | Resistor for tracking input voltage filter  | 10ΚΩ                                                          |                                           |

| C5 = C6        | Capacitor for Tracking input voltage filter | 1nF                                                           |                                           |

| C7 = C8        | Dc decoupling capacitor                     | 1μF                                                           |                                           |

| R13            | Bias Resistor for Stby/Mute function        | 10ΚΩ                                                          |                                           |

| R14            | Stby/Mute constant time resistor            | 30ΚΩ                                                          |                                           |

| R15            | Mute resistor                               | 30ΚΩ                                                          |                                           |

| C9             | Capacitor for Stby/Mute resistor            | 2.2μF                                                         |                                           |

| R16 = R17      | Sensing resistor for SOA detector           | 120mΩ<br>5% 4W                                                |                                           |

| R18            | Conversion resistor for threshold voltage   | 100ΚΩ                                                         |                                           |

| C10 = C11      | Power supply filter capacitor               | 100nF                                                         |                                           |

| R22 = R24      | Centering resistor                          | 400 $\Omega$ , 1W                                             |                                           |

| C12 = C13      | Tracking rail power supply filter           | 680nF                                                         |                                           |

| R19            | Protection                                  | 1ΚΩ                                                           |                                           |

| R20            | TRK_out                                     | 40ΚΩ                                                          |                                           |

| C14 = C15      | Power supply filter capacitor               | $470\mu\text{F},63\text{V}$                                   |                                           |

| C16 = C17      | Feedback capacitor                          | 100pF                                                         |                                           |

| D1             | Schottky diode                              | SB360                                                         |                                           |

Note: Vcontrol is the voltage at Att\_Rel pin.

### **APPLICATION HINTS**

#### PREAMPLIFIER AND COMPRESSOR

In the application circuit showed in figure 7,  $R_1/R_3$  (or  $R_2/R_4$ ) ratio fix the gain of the preamplifier.

If the input signal is very low, is possible to increase the gain fixing the product Vin\*G = cost.

In that case is possible to increase G decreasing  $R_{1,2}$  from  $10K\Omega$  until  $2K\Omega$  without relevant effects on the circuitbehavior and remaining in the operating range  $I_{in\_max} = V_{in\_max}/R_{1(2)}$ ,<1mA.

So it is possible to increase the preamplifier gain until 25.

If no compression is present (equivalnt compressor Gm=0), the effects are:

- The output voltage offset increase

- The SNR decrease

The following table shows these variations:

| R <sub>1,2</sub> | V <sub>IN MAX</sub> | G  | V <sub>OFFSET</sub> | EN   |

|------------------|---------------------|----|---------------------|------|

| 10ΚΩ             | 8V                  | 5  | 15mV                | 10μV |

| 5ΚΩ              | 4V                  | 10 | 30mV                | 13μV |

| 2ΚΩ              | 1.6V                | 25 | 75mV                | 20μV |

$R_{3(4)} = 50K\Omega$  and all the other external components are the same

Attenuation = 0 dB

If the compression is active the circuit behaviour is the same.

It's also possible to eliminate the compressor. In this case the ATT\_REL (1,2) pin must be connected to gnd.

### STBY-MUTE CIRCUIT

In the suggested application circuit (figure 7), the resistor for Standby/Mute function (R<sub>13</sub>) is connected between the Standby/Mute switches and 5V Supply.

It is possible to connect the resistor to another Supply Voltage level  $V_L$ , but in that case also the resistor value ( $R_{13,14}$ ) must be changed according to the following formula (fixing  $V_{STBY/MUTE} = 2.5V$  and  $R_{15} = 10K\Omega$ ):

$$R_{13} = (4 \cdot V_L - 10) K\Omega$$

$$R_{14} = (4 \cdot V_L + 10) K\Omega$$

#### **HEADROOM**

In the suggested application circuit the supply voltage to obtain 75W (Power Output) on  $8\Omega$  (R<sub>load</sub>) is:

$$V_{\text{supply}} = \Delta V + I_{L, MAX} \cdot R_{DSon}$$

It is also possible to increase the system's efficiency forcing the headroom to follow the output signal (variable drop insteadof a constant drop).

In that case:

$$V_{\text{supply}} = \Delta V + I_{L}(V) \cdot R_{DSon}$$

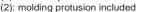

| DIM.   |            | mm    |       |       | inch  |       |

|--------|------------|-------|-------|-------|-------|-------|

| DIIVI. | MIN.       | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α      | 4.45       | 4.50  | 4.65  | 0.175 | 0.177 | 0.183 |

| В      | 1.80       | 1.90  | 2.00  | 0.070 | 0.074 | 0.079 |

| С      |            | 1.40  |       |       | 0.055 |       |

| D      | 0.75       | 0.90  | 1.05  | 0.029 | 0.035 | 0.041 |

| Е      | 0.37       | 0.39  | 0.42  | 0.014 | 0.015 | 0.016 |

| F (1)  |            |       | 0.57  |       |       | 0.022 |

| G      | 0.80       | 1.00  | 1.20  | 0.031 | 0.040 | 0.047 |

| G1     | 25.75      | 26.00 | 26.25 | 1.014 | 1.023 | 1.033 |

| H (2)  | 28.90      | 29.23 | 29.30 | 1.139 | 1.150 | 1.153 |

| H1     |            | 17.00 |       |       | 0.669 |       |

| H2     |            | 12.80 |       |       | 0.503 |       |

| H3     |            | 0.80  |       |       | 0.031 |       |

| L (2)  | 22.07      | 22.47 | 22.87 | 0.869 | 0.884 | 0.904 |

| L1     | 18.57      | 18.97 | 19.37 | 0.731 | 0.747 | 0.762 |

| L2 (2) | 15.50      | 15.70 | 15.90 | 0.610 | 0.618 | 0.626 |

| L3     | 7.70       | 7.85  | 7.95  | 0.303 | 0.309 | 0.313 |

| L4     |            | 5     |       |       | 0.197 |       |

| L5     |            | 3.5   |       |       | 0.138 |       |

| M      | 3.70       | 4.00  | 4.30  | 0.145 | 0.157 | 0.169 |

| M1     | 3.60       | 4.00  | 4.40  | 0.142 | 0.157 | 0.173 |

| N      |            | 2.20  |       |       | 0.086 |       |

| 0      |            | 2     |       |       | 0.079 |       |

| R      |            | 1.70  |       |       | 0.067 |       |

| R1     |            | 0.5   |       |       | 0.02  |       |

| R2     |            | 0.3   |       |       | 0.12  |       |

| R3     |            | 1.25  |       |       | 0.049 |       |

| R4     |            | 0.50  |       |       | 0.019 |       |

| V      |            |       |       | Гур.) | ·     |       |

| V1     | 3° (Typ.)  |       |       |       |       |       |

| V2     | 20° (Typ.) |       |       |       |       |       |

| V3     |            |       | 45° ( | Тур.) |       |       |

# **OUTLINE AND MECHANICAL DATA**

Flexiwatt27 (vertical)

(1): dam-bar protusion not included (2): molding protusion included

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

® 2003 STMicroelectronics - All Rights Reserved

**EASTITUTE** is the registered trademark and patented technology of INDIGO manufacturing inc.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States..

http://www.st.com

4