**DPS1035**

## 24V/3.5A 1-CH POWER SWITCH w/ REVERSE-VOLTAGE PROTECTION

## **Description**

The DPS1035 is part of a family of power switches optimized for the USB Type- $C^{TM}$  and other hot-swap applications. Through the analog interface, exception status is reported and functions like voltage limiting and output voltage ramp-up rate can be programmed.

This device is designed to operate between 4.5V and 24V. Its built-in fault-handling mechanism includes reverse voltage and current blocking, input over-voltage protection, and thermal shutdown. In addition, the ramp-up time of the output voltage can be adjusted to minimize in-rush current and to ensure system stability. Before any exception condition is notified via the low-active FAULTB signal, deglitch of 7ms is applied to prevent false triggering.

The DPS1035 is housed in the low-profile and space-saving V-QFN4040-17 package which is manufactured with environmentally friendly material.

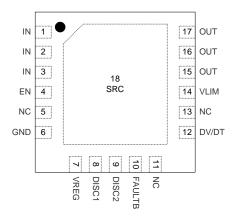

## **Pin Assignments**

### (Top View)

V-QFN4040-17

#### **Features**

- Wide Operating Voltage Range: 4.5V to 24V

- 1-Channel power switch with built-in fault detection and recovery mechanisms like input under-voltage lockout, reverse-voltage & current blocking, thermal shutdown and input over-voltage protection

- R<sub>DS(ON)</sub> of Embedded Power MOSFET at 30mΩ

- Adjustable DV/DT Control at Start-Up

- Manual Discharge ON/OFF Control for IN and OUT Ports

- Fault Reporting (FAULTB) with Blanking Time at 7ms Typical

- Totally Lead-free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen- & Antimony-free "Green" Device (Note 3)

# **Applications**

- Notebook, Desktop & AIO PCs; Servers and Tablets

- Docking Stations, Universal & Multimedia Hubs

- FPTVs, PC Monitors

- Set-Top-Boxes, Residential Gateways, Storage Devices

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of halogen- and antimony-free, "green" and lead-free.

- 3. Halogen- and antimony-free "green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

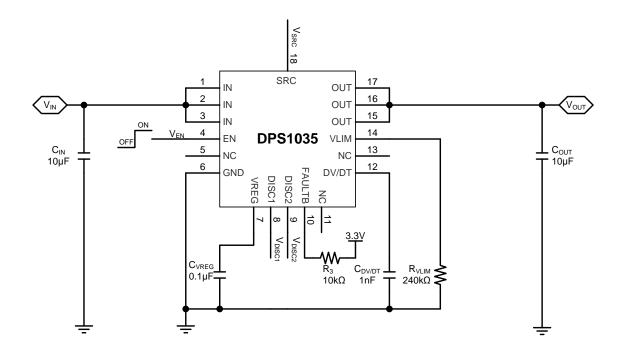

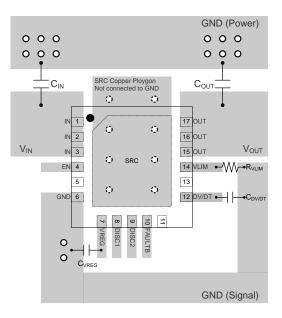

# **Typical Application Circuit**

# **Pin Descriptions**

| Pin Number          | Pin Name | Туре | Function                                                                                                                  |

|---------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3             | IN       | Р    | Power Supply and Input Port.                                                                                              |

| 4                   | EN       | 1    | Enable. '0' = device OFF; '1' = device ON. This pin must not be left floating.                                            |

| 5, 11, 13           | NC       | _    | No Connection. All NC pins must be left floating.                                                                         |

| 6                   | GND      | GND  | Device Ground                                                                                                             |

| 7                   | VREG     | I/O  | Voltage Regulator. A 0.1µF capacitor is recommended between this pin and ground.                                          |

| 8                   | DISC1    | 1    | IN Port Discharge Control. '1' = port voltage to be discharged; '0' = disabled.                                           |

| 9                   | DISC2    | 1    | OUT Port Discharge Control. '1' = port voltage to be discharged; '0' = disabled.                                          |

| 10                  | FAULTB   | 0    | Fault Status Indicator. An external pull-up resistor is required. This active-low pin shall be tied to GND when not used. |

| 12                  | DV/DT    | I/O  | Ramp-up Control. A capacitor between this pin and GND sets the ramp-up rate.                                              |

| 14                  | VLIM     | I/O  | Voltage Limit Setting. A resistor between this pin and GND sets the over-voltage limit of the IN port.                    |

| 15, 16, 17          | OUT      | 0    | Output Port.                                                                                                              |

| 18 (Exposed<br>Pad) | SRC      | I/O  | Common Source. The exposed pad of the V-QFN4040-17 package must not be connected to any signal.                           |

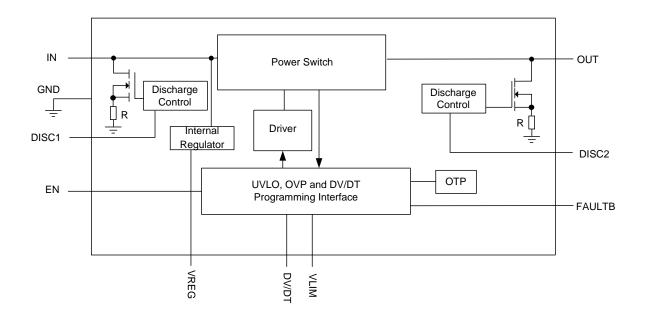

# **Functional Block Diagram**

# **Absolute Maximum Ratings** (@ $T_A = +25^{\circ}C$ , unless otherwise specified.) (Note 4)

| Symbol                             | Parameter                                                                    | Rating      | Unit |

|------------------------------------|------------------------------------------------------------------------------|-------------|------|

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage Range of IN and OUT Pins                                             | -0.3 to 30  | V    |

| V <sub>I/O</sub>                   | Voltage Range of Others (EN, VREG, DISC1, DISC2, FAULTB, DV/DT and VLIM Pin) | -0.3 to 6   | V    |

| I <sub>OUT</sub>                   | Output Load Current Range                                                    | 5           | Α    |

| TJ                                 | Operating Junction Temperature                                               | -40 to 125  | °C   |

| TL                                 | Lead Temperature                                                             | 260         | °C   |

| T <sub>ST</sub>                    | Storage Temperature                                                          | -65 to +150 | °C   |

| ESD                                | Human Body Model (HBM), JESD22-A114                                          | 2           | kV   |

| ESD                                | Charge Device Model (CDM)                                                    | 0.5         | T KV |

Note:

# Thermal Characteristics (@ T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 5)

| Symbol           | Parameter                               | Rating | Unit |

|------------------|-----------------------------------------|--------|------|

| $P_{D}$          | Power Dissipation                       | 2.1    | W    |

| $R_{	heta JA}$   | Thermal Resistance, Junction-to-Ambient | 58.5   | °C/W |

| R <sub>eJC</sub> | Thermal Resistance, Junction-to-Case    | 9.4    | °C/W |

Note:

5. Device mounted on FR-4 substrate PC board, 2oz copper, with 1"x1" copper pad layout.

<sup>4.</sup> These are stress ratings only. Operation outside the absolute maximum ratings may cause device failure. Operation at the absolute maximum rating for extended periods may reduce device reliability.

# Recommended Operating Conditions (@ T<sub>A</sub> = +25°C, unless otherwise specified)

| Symbol                                  | Parameter                        | Min | Max | Unit |

|-----------------------------------------|----------------------------------|-----|-----|------|

| V <sub>IN</sub>                         | Input Supply Voltage             | 4.5 | 24  | V    |

| V <sub>OUT</sub>                        | Output Voltage                   | 0   | 24  | V    |

| lout                                    | Output Load Current              | 0   | 3.5 | А    |

| C <sub>IN</sub>                         | Input Capacitance                | 1   | _   | μF   |

| C <sub>OUT</sub>                        | Output Capacitance               | 1   | _   | μF   |

| V <sub>EN</sub>                         | Input Voltage on EN              | 0   | 5   | V    |

| V <sub>DISC1</sub> , V <sub>DISC2</sub> | Input Voltage on DISC1 and DISC2 | 0   | 5.5 | V    |

# **Electrical Characteristics**

$\underline{\text{(@T_A = +25^{\circ}C, V_{IN} = 4.5V to 24V, C_{IN} = C_{OUT} = 10\mu\text{F}, V_{EN} = 3.3V, C_{DV/DT} = 1n\text{F}, R_{VLIM} = 240k\Omega, unless otherwise specified.)}}$

| Symbol                | Parameter                                                                     | Conditions                                                           | Min | Тур  | Max | Unit |  |

|-----------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------|-----|------|-----|------|--|

| Bias Supply           | •                                                                             |                                                                      |     | •    | •   |      |  |

| V <sub>UVLO</sub>     | V <sub>IN</sub> Under-Voltage Lockout<br>Threshold                            | V <sub>IN</sub> Rising                                               | 3.2 | 3.7  | 4   | V    |  |

| $V_{\text{UVHY}}$     | V <sub>IN</sub> Under-Voltage Lockout<br>Threshold Hysteresis                 | V <sub>IN</sub> Falling                                              | _   | 250  | _   | mV   |  |

|                       |                                                                               | $V_{IN} = 5V, V_{EN} = 0V$                                           | _   | _    | 10  |      |  |

| I <sub>SHDN</sub>     | Shutdown Current (Disabled)                                                   | $V_{IN} = 12V, V_{EN} = 0V$                                          | _   | _    | 25  | μΑ   |  |

|                       |                                                                               | $V_{IN} = 20V, V_{EN} = 0V$                                          | _   | _    | 50  |      |  |

|                       |                                                                               | V <sub>IN</sub> = 5V, No Load                                        | _   | _    | 3   |      |  |

| IQ                    | Quiescent Current (Enabled)                                                   | V <sub>IN</sub> = 12V, No Load                                       | _   | _    | 4   | mA   |  |

|                       |                                                                               | V <sub>IN</sub> = 20V, No Load                                       | _   | _    | 4.5 |      |  |

| Enable Conti          | rol                                                                           |                                                                      |     |      |     |      |  |

| V <sub>ENL</sub>      | EN Threshold Voltage Low                                                      | V <sub>EN</sub> Falling                                              | _   | _    | 0.4 | \/   |  |

| V <sub>ENH</sub>      | EN Threshold Voltage High                                                     | V <sub>EN</sub> Rising                                               | 1.4 | _    | _   | V    |  |

| I <sub>EN</sub>       | EN Input Leakage Current                                                      | V <sub>IN</sub> = 5V, V <sub>EN</sub> = 5V                           | _   | _    | 1   | μΑ   |  |

| Over-Voltage          | Protection                                                                    |                                                                      | •   | •    | •   | •    |  |

| I <sub>VLIM</sub>     | V <sub>LIM</sub> Sourcing Current                                             | $V_{IN} = 5V$ , $R_{VLIM} = 57.6k\Omega$                             | _   | 10   |     | μA   |  |

| R <sub>VLIM_MAX</sub> | Maximum R <sub>VLIM</sub>                                                     | _                                                                    | _   | _    | 300 | kΩ   |  |

|                       | Input Over-Voltage Threshold, Rising                                          | $R_{VLIM} = 57.6k\Omega$ , $V_{IN}$ Rising                           | _   | 6    | _   |      |  |

| Vovprth               |                                                                               | R <sub>VLIM</sub> = 240kΩ, V <sub>IN</sub> Rising                    | _   | 24   | _   | .,   |  |

|                       | Input Over-Voltage Threshold,                                                 | $R_{VLIM} = 57.6k\Omega$ , $V_{IN}$ Falling                          | _   | 5.6  | _   | V    |  |

| $V_{OVPFTH}$          | Falling                                                                       | R <sub>VLIM</sub> = 240kΩ, V <sub>IN</sub> Falling                   | _   | 23.6 | _   |      |  |

| MOSFET                | •                                                                             |                                                                      |     | •    | •   |      |  |

|                       |                                                                               | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 1A                          | _   | 30   | 40  |      |  |

| R <sub>DS(ON)</sub>   | Switch ON Resistance                                                          | V <sub>IN</sub> = 12V, I <sub>OUT</sub> = 1A                         | _   | 30   | 40  | mΩ   |  |

| , ,                   |                                                                               | V <sub>IN</sub> = 20V, I <sub>OUT</sub> = 1A                         | _   | 30   | 40  | 1    |  |

| I <sub>LKGSRC</sub>   | OUT Leakage Current in OFF State, Sourcing                                    | V <sub>EN</sub> = 0V, V <sub>OUT</sub> =0V                           | _   | _    | 1   | μΑ   |  |

|                       | 0.17.                                                                         | $V_{IN} = 3.3V, V_{EN} = 0V, V_{OUT} = 5V$                           | _   | _    | 1   |      |  |

| I <sub>LKGSNK</sub>   | OUT Leakage Current in OFF State, Sinking                                     | V <sub>IN</sub> = 3.3V, V <sub>EN</sub> = 0V, V <sub>OUT</sub> = 12V | _   | _    | 1   | μA   |  |

|                       | State, Sinking                                                                | $V_{IN} = 3.3V$ , $V_{EN} = 0V$ , $V_{OUT} = 20V$                    | _   | _    | 1   |      |  |

| Reverse-Volt          | age Protection                                                                |                                                                      |     |      |     |      |  |

| V <sub>RVPFTH</sub>   | V <sub>IN</sub> - V <sub>OUT</sub> Threshold Entering into Reverse Protection | V <sub>IN</sub> - V <sub>OUT</sub> Falling                           | _   | -40  | _   | mV   |  |

| V <sub>R</sub> VPRTH  | V <sub>IN</sub> - V <sub>OUT</sub> Threshold Exiting from Reverse Protection  | V <sub>IN</sub> - V <sub>OUT</sub> Rising                            | -15 | 0    | _   | IIIV |  |

| t <sub>RVPTD</sub>    | Reverse Protection Response<br>Time                                           | _                                                                    |     | _    | 2   | μs   |  |

# **Electrical Characteristics** (Continued)

$(@T_A = +25 ^{\circ}C,\ V_{IN} = 4.5 \text{V to 24V},\ C_{IN} = C_{OUT} = 10 \mu\text{F},\ V_{EN} = 3.3 \text{V},\ C_{DV/DT} = 1 \text{nF},\ R_{VLIM} = 240 \text{k}\Omega,\ unless otherwise specified.})$

| Symbol                                       | Parameter                             | Conditions                                                             | Min | Тур  | Max | Unit |  |

|----------------------------------------------|---------------------------------------|------------------------------------------------------------------------|-----|------|-----|------|--|

| Output Ramp                                  | Output Ramping Control                |                                                                        |     |      |     |      |  |

| I <sub>DV/DT</sub>                           | DV/DT Sourcing Current                | $V_{DV/DT} = 0V$                                                       | _   | 1    | _   | μΑ   |  |

| G <sub>DV/DT</sub>                           | DV/DT to OUT Gain                     | ΔV <sub>OUT</sub> / ΔV <sub>DV/DT</sub> , Guaranteed by Design         | _   | 12   | _   | V/V  |  |

| <b>Output Timin</b>                          | g                                     |                                                                        |     |      |     |      |  |

|                                              |                                       | $V_{IN} = 5V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 0V$ to $2V$             | _   | 0.2  | _   | ms   |  |

| $t_{DON}$                                    | Output Turn-ON Delay Time             | $V_{IN} = 12V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 0V$ to $2V$            | _   | 0.2  | _   |      |  |

|                                              |                                       | $V_{IN} = 20V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 0V$ to $2V$            | _   | 0.2  | _   |      |  |

|                                              |                                       | $V_{IN} = 5V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 0V$ to $2V$             | _   | 0.3  | _   |      |  |

| $t_R$                                        | Output Turn-ON Rise Time              | $V_{IN} = 12V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 0V$ to $2V$            | _   | 0.8  | _   | ms   |  |

|                                              |                                       | $V_{IN} = 20V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 0V$ to $2V$            | _   | 1.6  | _   |      |  |

|                                              |                                       | $V_{IN} = 5V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 2V$ to $0V$             | _   | 1    | _   |      |  |

| t <sub>DOFF</sub>                            | Output Turn-OFF Delay Time            | $V_{IN} = 12V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 2V$ to $0V$            | _   | 2    | _   | μs   |  |

|                                              |                                       | $V_{IN} = 20V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 2V$ to $0V$            | _   | 4    |     |      |  |

|                                              |                                       | $V_{IN} = 5V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 2V$ to $0V$             | _   | 10   | _   |      |  |

| t <sub>F</sub>                               | Output Turn-OFF Fall Time             | $V_{IN} = 12V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 2V$ to $0V$            | _   | 25   | _   | μs   |  |

|                                              |                                       | $V_{IN} = 20V$ , $C_{OUT} = 1\mu F$ , $V_{EN} = 2V$ to $0V$            | _   | 50   | _   |      |  |

| Discharge Co                                 | ontrol on IN/OUT Pins                 |                                                                        |     | •    |     |      |  |

|                                              | IN/OUT Disable and Desistance         | V <sub>DISC1</sub> = 5V, V <sub>DISC2</sub> = 5V                       | _   | 70   | _   | Ω    |  |

| R <sub>DISC1/DISC2</sub>                     | IN/OUT Discharge Resistance           | V <sub>DISC1</sub> = 3.3V, V <sub>DISC2</sub> = 3.3V                   | _   | 82   | _   | Ω    |  |

| V <sub>DISC1L</sub> /<br>V <sub>DISC2L</sub> | DISC1/DISC2 Threshold<br>Voltage Low  | V <sub>DISC1</sub> /V <sub>DISC2</sub> Falling                         | _   | _    | 0.4 | ٧    |  |

| V <sub>DISC1H</sub> /<br>V <sub>DISC2H</sub> | DISC1/DISC2 Threshold<br>Voltage High | V <sub>DISC1</sub> /V <sub>DISC2</sub> Rising                          | 1.4 | _    | _   | V    |  |

| Fault Flag (FAULTB): Active Low              |                                       |                                                                        |     |      |     |      |  |

| R <sub>FAULTB</sub>                          | FAULTB Pull-Down Resistor             | $V_{IN} = 7V$ , $R_{VLIM} = 57.6k\Omega$ , $I_{FAULTB} = 10mA$ Sinking | _   | 25   | _   | Ω    |  |

| ILKGFAULTB                                   | FAULTB Leakage Current                | $V_{IN} = 5V$ , $R_{VLIM} = 57.6k\Omega$ , $V_{FAULTB} = 5V$           | _   | _    | 1   | μΑ   |  |

| t <sub>BLANKFAULTB</sub>                     | FAULTB Blanking Time                  | $V_{IN} = 5V$ , $R_{VLIM} = 57.6k\Omega$ , $V_{FAULTB} = 5V$           | _   | 7    | _   | ms   |  |

| Thermal Shut                                 | down                                  | •                                                                      | •   | •    |     | •    |  |

| T <sub>SHDN</sub>                            | Thermal Shutdown Threshold            | _                                                                      | _   | +155 | _   | °C   |  |

| T <sub>HYS</sub>                             | Thermal Shutdown Hysteresis           | _                                                                      | _   | +20  | _   | °C   |  |

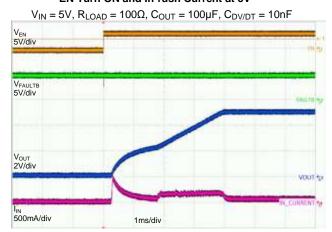

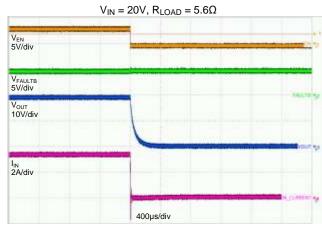

## **Performance Characteristics**

(@T<sub>A</sub> = +25°C, C<sub>IN</sub> = C<sub>OUT</sub> = 10 $\mu$ F, V<sub>EN</sub> = 3.3V, C<sub>DV/DT</sub> = 1nF, R<sub>VLIM</sub> = 240k $\Omega$ , unless otherwise specified.)

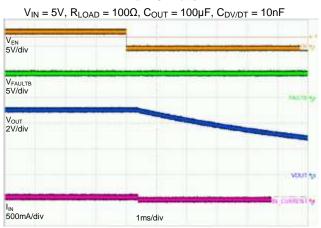

### **EN Turn ON and In-rush Current at 5V**

### **EN Turn OFF at 5V**

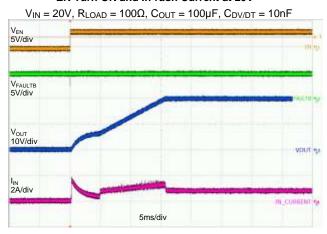

### EN Turn ON and In-rush Current at 20V

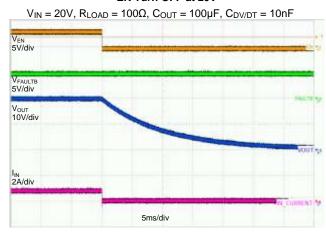

### **EN Turn OFF at 20V**

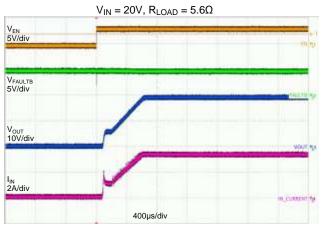

## EN Turn ON with a 5.6Ω Load at 20V

## EN Turn OFF with a $5.6\Omega$ Load at 20V

# **Application Information**

### **General Description**

The DPS1035 is an unidirectional power switch designed to meet the input and output voltage/current requirement which is common with many hot-pluggable serial interfaces found in the computing and consumer electronics equipment.

#### Ramp-Up Time and In-Rush Current Control

An external capacitor connected from the DV/DT pin to GND defines the slew rate of the output voltage at power-on:

$$dV_{OUT}$$

/  $dt = (I_{DV/DT} / C_{DV/DT}) \times G_{DV/DT}$ , where  $I_{DV/DT} = 1\mu A$  typ. and  $G_{DV/DT} = 12$

The total ramp-up time t<sub>DV/DT</sub> of V<sub>OUT</sub>, increasing from 0 to V<sub>IN</sub>, can be calculated using the following equation:

$$t_{DV/DT} = 8.3 \times 10^4 \times V_{IN} \times C_{DV/DT}$$

The in-rush current at power-up shall be limited by the regulated output voltage ramp.

#### Input Over-Voltage Protection (OVP)

The voltage at the IN port is monitored continuously. Whenever voltage at the IN port is found to be larger than the V<sub>OVPRTH</sub> value, the built-in over-voltage protection (OVP) fault-handling mechanism is triggered. The internal power MOSFET will be turned OFF to protect the downstream equipment connected. The V<sub>OVPRTH</sub> value is determined by:

$V_{OVPRTH} = 0.1 \times R_{VLIM}$ , where the unit of  $R_{VLIM}$  is  $k\Omega$  and  $51k\Omega \le R_{VLIM} \le 240k\Omega$ .

#### **Over-Temperature Protection (OTP)**

When the junction temperature T<sub>J</sub> reaches the thermal shutdown threshold T<sub>SHDN</sub>, the internal power MOSFET would be turned OFF. The internal power MOSFET will be turned ON again once the condition [T<sub>J</sub> < (T<sub>SHDN</sub> - T<sub>HYS</sub>)] becomes valid.

### Reverse-Voltage Protection (RVP)

The voltage difference,  $[V_{IN} - V_{OUT}]$ , between the IN and OUT ports is monitored continuously. Once the voltage difference drops below the  $V_{RVPFTH}$  level, the device shall immediately turn OFF the internal power MOSFET to prevent the current flowing from the opposite direction. When the reverse-voltage condition is no longer valid, i.e.  $[V_{IN} - V_{OUT}]$  becomes greater than the  $V_{RVPRTH}$  level, the internal power MOSFET shall be turned ON.

#### **Fault Response**

An external pull-up resistor is required. The device generates a warning flag whenever one of the following fault conditions becomes valid: input over-voltage, reversed-voltage, over-temperature. After a de-glitch time-out of 7ms, the low-active FAULTB signal shall be asserted. The FAULTB signal shall remain 'low' and the internal power MOSFET remains OFF until the exception status is no longer valid.

#### **Discharge Function**

To facilitate the various applications envisioned by the system designers, the IN and OUT ports can be discharged via two external controls: DISC1, DISC2. The internal discharge resistor is around  $80\Omega$ . The settings are shown in the table below.

| DISC1 | DISC2 | Description                                                      |

|-------|-------|------------------------------------------------------------------|

| 0     | 0     | Discharge function disabled                                      |

| 0     | 1     | OUT Port is being discharged until the pin DISC2 is pulled 'low' |

| 1     | 0     | IN Port is being discharged until the pin DISC1 is pulled 'low'  |

| 1     | 1     | Both IN and OUT ports are discharged simultaneously              |

# **Application Information (Continued)**

## **PCB Layout Consideration**

- 1. Place the input and output capacitors, C<sub>IN</sub> and C<sub>OUT,</sub> as close as possible to the IN and OUT pins.

- 2. The power traces, including the power ground, the  $V_{IN}$  trace and the  $V_{OUT}$  trace should be kept direct, short and wide.

- 3. Place the resistors and capacitors (R<sub>VLIM</sub>, C<sub>DV/DT</sub> and C<sub>VREG</sub>) as close as possible to the corresponding device pins.

- 4. Connect the signal ground to the GND pin, and keep a single connection from GND pin to the power ground behind the input capacitor.

- 5. For better power dissipation, via holes are recommended to connect the exposed pad's landing area to a large copper polygon on the other side of the printed circuit board. The copper polygons and exposed pad of SRC (common source nodes of internal power MOSFET) shall not be connected to any of the signal and power grounds on the printed circuit board.

Figure 1 Suggested PCB Layout

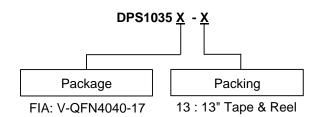

# **Ordering Information** (Note 6)

| Part Number   | Marking | Reel Size (inches) | Tape Width (mm)    | 13" Tape and Reel |                    |  |

|---------------|---------|--------------------|--------------------|-------------------|--------------------|--|

| Fait Number   |         |                    | rape width (illin) | Quantity          | Part Number Suffix |  |

| DPS1035FIA-13 | DPS1035 | 13                 | 12                 | 4,000/Tape & Reel | -13                |  |

Note: For packaging details, go to our website at http://www.diodes.com/products/packages.html.

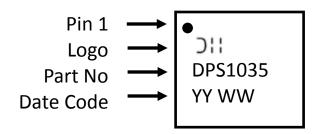

# **Marking Information**

YY: Year

WW: Week 01~52; 52

represents 52 and 53 week

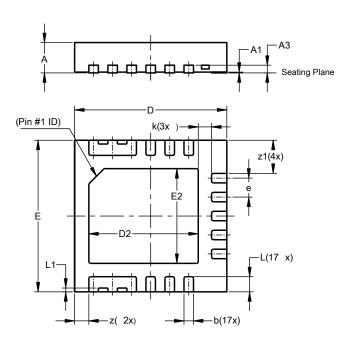

# **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

## V-QFN4040-17

| V-QFN4040-17         |       |         |       |  |  |

|----------------------|-------|---------|-------|--|--|

| Dim                  | Min   | Max     | Тур   |  |  |

| Α                    | 0.75  | 0.85    | 0.80  |  |  |

| A1                   | 0.00  | 0.05    | 0.02  |  |  |

| A3                   | _     | _       | 0.203 |  |  |

| b                    | 0.20  | 0.30    | 0.25  |  |  |

| D                    | 3.95  | 4.05    | 4.00  |  |  |

| D2                   | 2.775 | 2.975   | 2.875 |  |  |

| E                    | 3.95  | 4.05    | 4.00  |  |  |

| E2                   | 2.40  | 2.60    | 2.50  |  |  |

| е                    | C     | ).50 BS | С     |  |  |

| k                    | _     | _       | 0.35  |  |  |

| L1                   | _     | _       | 0.10  |  |  |

| L                    | 0.35  | 0.45    | 0.40  |  |  |

| Z                    | _     | _       | 0.38  |  |  |

| z1                   | _     | _       | 0.88  |  |  |

| All Dimensions in mm |       |         |       |  |  |

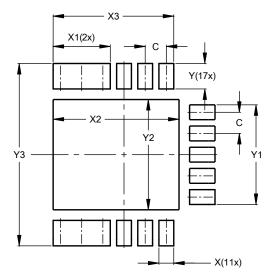

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

## V-QFN4040-17

| Dimensions | Value (in mm) |

|------------|---------------|

| С          | 0.500         |

| X          | 0.350         |

| X1         | 1.350         |

| X2         | 2.975         |

| Х3         | 2.850         |

| Υ          | 0.600         |

| Y1         | 2.350         |

| Y2         | 2.600         |

| Y3         | 4.300         |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2017, Diodes Incorporated

www.diodes.com